基于Xilinx的时序分析与约束(2)----基础概念(上)

judy 在 周三, 08/31/2022 - 09:37 提交

数字电路根据逻辑功能的不同特点,可以分成两大类:组合逻辑电路与时序逻辑电路

数字电路根据逻辑功能的不同特点,可以分成两大类:组合逻辑电路与时序逻辑电路

这个专栏,我会从时序分析、时序约束和时序收敛3个方面来一起学习基于Xilinx FPGA和Vivado开发平台的FPGA时序相关内容。

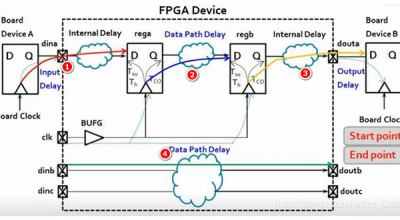

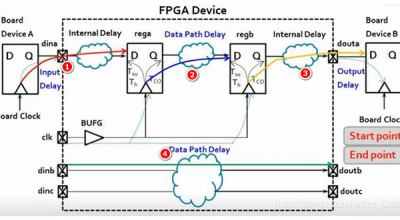

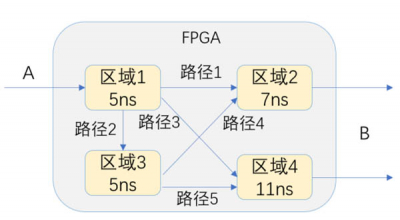

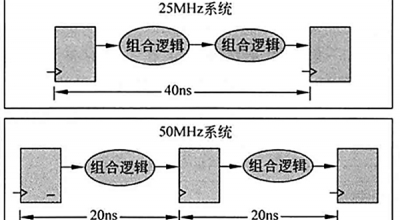

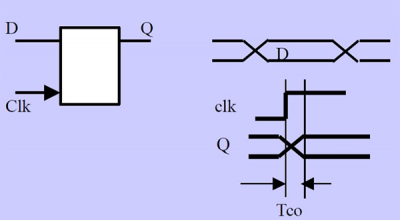

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。

传播延时,即I/O管脚输入到非寄存器输出延时。信号从任何一个I/O脚输入,通过一个宏单元内的组合逻辑后,从另一个管脚输出,所需要的时间。范围:5~12ns。

发起沿和捕获沿(Launch edge & Capture edge)

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。

这次的练习选择的是ZYNQ的芯片,原本工程是工作在100MHz的时钟,但是作为练习,我们可以把时钟调到一个极限的程度来进行优化。