Vitis AI 用户指南 v3.5

judy 在 周二, 01/02/2024 - 17:46 提交

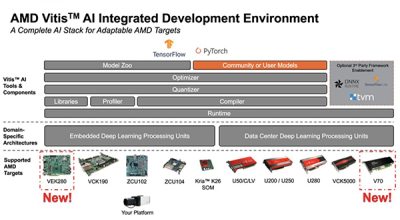

本指南旨在描述 AMD Vitis™ AI 开发套件,它属于全栈深度学习 SDK,适用于深度学习处理单元。

本指南旨在描述 AMD Vitis™ AI 开发套件,它属于全栈深度学习 SDK,适用于深度学习处理单元。

本用户指南涵盖了 Vitis 入门、使用 Vitis Unified IDE、Bootgen 工具

为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado™ 时序收敛

本文档旨在逐步指导您熟悉各种 Vitis 工具,这些工具采用自下而上的设计流程来开发系统组件

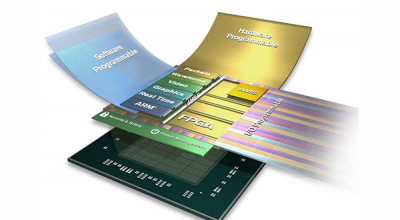

Vitis 工具可在各种不同的设计流程内为异构系统提供编译、链接、剖析和调试功能

FPGA 技术支持灵活开展现场编程和再编程,无需通过设计修改来重建互连结构

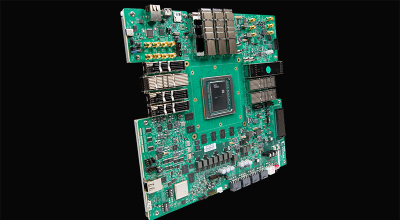

AMD首款 ASIC 级架构,不仅支持数百 Gb 级的系统性能,在全线路速度下支持智能处理

本文档涵盖了以下设计进程:机器学习和数据研究——将机器学习模型从 PyTorch、TensorFlow

本文详细描述了VPK180评估板的功能