Vitis 高级综合用户指南 (v2021.2)

judy 在 周五, 11/19/2021 - 15:49 提交

本文描述如何使用 Vitis™ 高级综合工具。

本文描述如何使用 Vitis™ 高级综合工具。

本文描述 AI引擎的编程环境。

Kria KV260视觉AI入门套件是一个开箱即用平台,开发人员可以通过首选设计环境,在任何抽象层添加定制和差异化功能,包括应用软件、AI模型乃至FPGA设计。本文描述了Kria™ KV260 Vision AI启动套件。

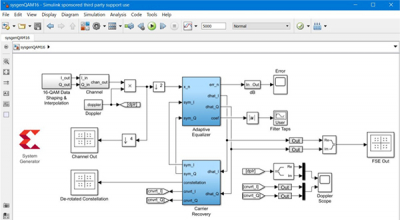

本文描述如何执行基于模型的设计,在 Simulink 环境中实现快速设计探索,并通过自动代码生成加速 Xilinx 器件的生产路径。

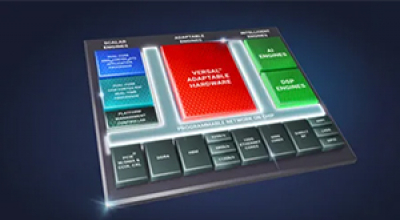

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。本指南将分为以下五大章节,遵循指南里的步骤和最佳实践进行操作,将有助于您以尽可能最快且最高效的方式实现期望设计目标。

SmartLynq+ 模块的构建旨在满足高速调试和跟踪需求,主要面向使用Versal™ 平台的开发者。与此前的赛灵思调试产品相比,SmartLynq+ 模块通过 HSDP 可将 Linux下载时间加快高达28倍,将数据捕获速度提高100倍。更快的迭代和重复下载既提高了开发效率,也缩短了设计周期。

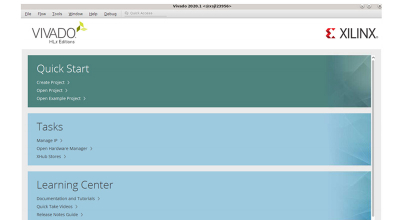

本文介绍 Vivado® 集成设计环境 (IDE),它提供了直观的图形用户界面 (GUI),用于可视化和与 FPGA 设计交互。描述了Vivado IDE如何帮助您配置工具选项、分析和完善时序,以及设计平面图以改进结果。

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

本文档旨在记述用于对赛灵思 FPGA 设计进行编程和调试的 Vivado® 工具。FPGA 编程包括从已实现的设计生成比特流文件和将此文件下载至目标器件。本文档还描述了如何进行设计调试,包括 RTL 仿真和系统内调试。

本文详细描述了 VCK190 评估板的功能。使用本指南开发和评估VCK190板上针对Versal ACAP XCVC1902器件的设计。