全新 Spartan UltraScale+ FPGA 系列 - 以小型封装实现高 I/O 和低功耗

judy 在 周三, 03/20/2024 - 09:42 提交

Spartan UltraScale+ FPGA 低成本系列带来出色的 I/O 逻辑单元比

Spartan UltraScale+ FPGA 低成本系列带来出色的 I/O 逻辑单元比

Spartan UltraScale+ 器件能为边缘端各种 I/O 密集型应用提供成本效益与高能效性能

一种面向 FPGA 的大模型轻量化部署流程FlightLLM

在Ultrascale+ HBM系列的器件上包含有容量32Gb/64Gb的高带宽硬件存储介质HBM

在一些系统安全性要求较高的设计里,通常会加入系统自检功能

SEM IP将错误大致分为两类,可纠和不可纠

Alveo™ U45N 网络加速器是一款基于 FPGA 的平台,可为数据中心的基础架构工作负载提供低时延

UltraScale / UlraScale+系列的SEM IP一共有6种工作模式

该新系列非常适合需要低功耗和高 I/O 的成本敏感型应用,其面向广泛的行业

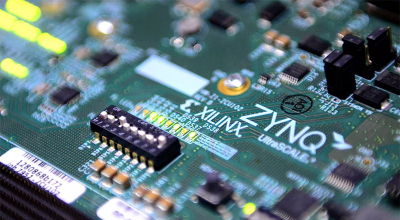

Zynq UltraScale+ PS MIO 可能在 VCCO_PSMIO 电源上电缓升期间输出高位毛刺