AMD Vivado Hardware Debug 技巧-如何在下载 Bitstream 后自动触发 ILA 采集

judy 在 周五, 02/23/2024 - 10:57 提交

本文将介绍一种可适用于上述场景的方法,即在下载 Bitstream 后自动触发 ILA 采集,为硬件调试提供更多便利。

Virtex® UltraScale™ FPGA 是赛灵思(Xilinx)推出的一种高性能 FPGA 系列,采用先进的 UltraScale 架构。该系列 FPGA 具有卓越的性能和灵活性,广泛应用于各种高性能计算、数据中心、通信和其他领域。

Virtex UltraScale FPGA 系列为设计人员提供了强大的工具和资源,以满足对高性能、低功耗、灵活性和可扩展性的需求。

本文将介绍一种可适用于上述场景的方法,即在下载 Bitstream 后自动触发 ILA 采集,为硬件调试提供更多便利。

Alveo UL3524 带来了7倍的时延提升 ,从而达到小于3纳秒的FPGA收发器时延

千兆以太网解决方案利用Xilinx提供的AXI_1G/2.5G Ethernet SubSystem IP核来实现MAC功能

本文提出一种细粒度流水线结构以实现较高的DSP效率。

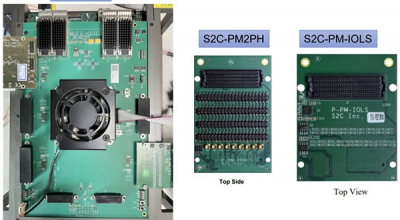

Sirius Wireless 的 Wi-Fi6/BT 射频 IP 验证系统基于思尔芯芯神瞳 S7-9P逻辑系统构建

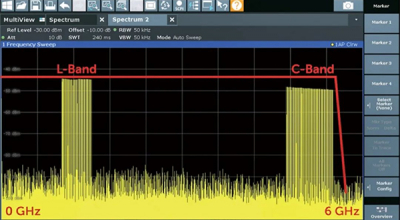

具有超宽模拟带宽的高采样率DAC和ADC是实现全数字多波段SAR系统的关键技术

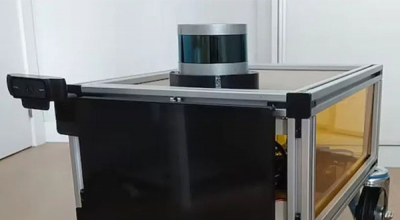

FX Shuttle 800 FPGA 加速盒子基于 Xilinx 的 Virtex UltraScale+ XCVU13P FPGA 芯片

本文详细介绍基于北京芯加速科技的VU13P平台,使用AXI Chip2Chip IP,开发测试了一套用于ASIC验证仿真的片间通信方案。

该项目基于AMD Xilinx Varium C1100 FPGA加速卡,为 Filecoin 区块链应用中的Poseidon哈希算法提供了一套完整的硬件加速方案。

最近,在ACM的FPGA 2022会议上发表了一篇题为“RapidStream: FPGA HLS设计的并行物理实现”的论文,论文中描述了一种非常有趣的方法,通过FPGA设计软件推动HLS设计更快地运行在多核处理器上。