检查功耗约束

judy 在 周一, 08/09/2021 - 09:34 提交

了解如何在 Versal™ACAP 设计中增加功耗和环境约束,以及如何利用 Vivado® Design Suite 的功耗和时序分析功能。

了解如何在 Versal™ACAP 设计中增加功耗和环境约束,以及如何利用 Vivado® Design Suite 的功耗和时序分析功能。

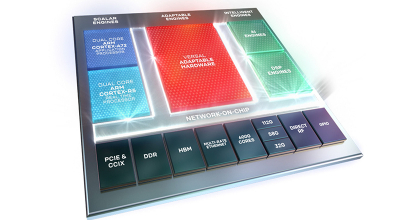

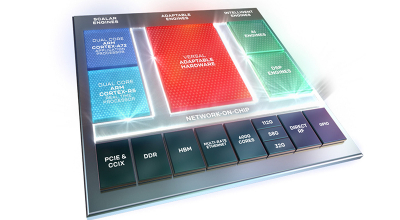

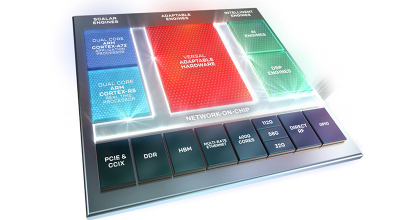

Xilinx 的 16nm FPGA、SoC 和 7nm Versal™ ACAP 以硬化模块及软 IP 形式提供多种架构组件,这使得它们成了设计新一代安全设备的理想之选。这些 IP 包括高速串行解串器和多速率接口 IP,例如硬化 MAC、PCIe® 接口和内存控制器等。

VERSALDEMO1Z 是一个和 Xilinx 联合开发的电源参考板,它为 Xilinx Versal ACAP 平台提供完整的电源轨,ACAP 平台包括自适应引擎、人工智能引擎和标量引擎,以及外部的 DDR 存储器。这款参考板已经开放订购,它既可以作为成熟的整套参考设计,帮助客户抢占设计先机,也可以作为评估平台,快速方便地进行电源测试。

在 aarch32 模式下,如果执行的代码包含下面的加密指令序列,并且在执行第一条加密指令后立即断言并中断,ELR 会被记录为返回地址,产生的错误可能会导致数据损坏

本答复记录旨在描述在 Versal ACAP 器件上使用物理不可克隆功能 (Physically Unclonable Function,PUF) 时,与 VCC_PMC 电源轨相关的要求。

每个 RPU 处理器都有 1 个 DBGDRAR 寄存器,其中包含 CoreSight 根 ROM 表的地址。但读取此寄存器时会返回错误的地址 0xfe800003。正确的返回地址应为 0xf0800003。尝试访问包含错误地址的 CoreSight 根 ROM 表将导致 RPU 处理器发生软件异常。

SmartLynq+ 模块教程视频介绍了如何在 Versal ACAP 设计中包括高速调试端口,并演示了 SmartLynq+ 模块配置和 Linux 映像下载流程。

处理器可使用等待事件 (wait for event, WFE) 或等待中断 (wait for interrupt, WFI) 机制来进入低功耗状态。仅当嵌入式跟踪宏单元 (Embedded Trace Macrocell, ETM) 耗尽 AMBA ATB 接口上的所有跟踪字节后,处理器才能进入低功耗状态。

本文提供Versal™ ACAP编程和设计的软件专用信息。

本文提供有关 Versal™ ACAP 集成块 for PCI Express® 内核的详细信息,IP 性能和资源利用率数据。