Versal ACAP VCK190基础目标参考设计

judy 在 周四, 09/09/2021 - 15:43 提交

体现 Versal 器件价值主张的参考设计。平台设计包括针对不同市场的视频、机器学习和基于 100G 以太网的 IP。用户可以按原样使用这些设计,也可以根据应用需求对其进行修改。

体现 Versal 器件价值主张的参考设计。平台设计包括针对不同市场的视频、机器学习和基于 100G 以太网的 IP。用户可以按原样使用这些设计,也可以根据应用需求对其进行修改。

Versal™ 自适应计算加速平台 (ACAP) 将标量引擎 (Scalar Engine)、自适应引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine) 与领先的存储器和交互技术有机结合,从而为任何应用提供强大的异构加速功能。Versal 架构 PCB 准则已基于前几代进行了精简,以方便 PCB 布局专业人员和硬件设计师使用。

本文介绍 DPUCVDX8G,这是一种可配置的计算引擎,针对具有 AI 引擎的 Versal ACAP 设备中的卷积神经网络进行了优化。

7月23日,Xilinx最新发布了Vitis AI 1.4版本,该版本在原有的AI加速解决方案基础上,首次增加了对Xilinx 7nm Versal ACAP两款平台VCK190,VCK5000 PCI-E卡,及16nm Kria SOM平台的支持,使得这一AI推理加速方案更加完整、灵活、强大。

在 Vivado 2021.1 中,Control, Interfaces and Processing System (CIPS) IP 架构已重新设计。此次升级支持将来自其它 Versal 系列的器件集成到 CIPS IP 内。

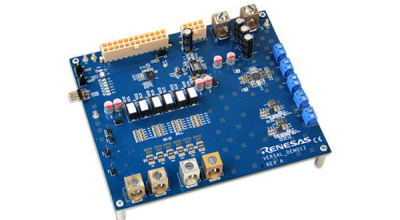

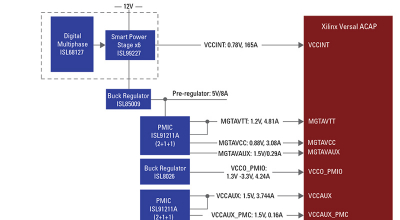

VERSALDEMO1Z 是一个和 Xilinx 联合开发的电源参考板,它为 Xilinx Versal ACAP 平台提供完整的电源轨,ACAP 平台包括自适应引擎、人工智能引擎和标量引擎,以及外部的 DDR 存储器。这款参考板已经开放订购,它既可以作为成熟的整套参考设计,帮助客户抢占设计先机,也可以作为评估平台,快速方便地进行电源测试。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件。除了误报此错误外,并未观测到任何功能性问题,且仍可继续使用 LSO 卸载功能。

如果 Arm Cortex-A72 处理器配置为向处于 UniqueClean (UC) 状态的缓存行发送逐出传输事务,那么 Cortex-A72 处理器可能返回陈旧数据并发出嗅探响应。

Versal 自适应计算加速平台(ACAP)是 Xilinx 最新的 SoC 片上系统系列之一。它包含了标量处理引擎、适配硬件、(软件可编程和硬件可调整)智能引擎和片上网络,即一个软件可编程基础架构。这需要适应能力很强的精确时序和电源。

每个 RPU 处理器都有 1 个 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,读取 RPU 的 DBGDSAR 寄存器会返回以下不正确的偏移值: