Versal ACAP,APU - 持续逐出与互连反压相结合可能导致写回无分配存储发生停滞

judy 在 周五, 06/04/2021 - 09:24 提交

在任何一致的 ACE 系统中,启用 WriteUnique/WriteLineUnique (WU/WLU) 传输事务后,如果在有一项或多项高速缓存逐出事务处于暂挂状态时尝试执行存储,那么写回无分配 (WBNA) 存储可能发生停滞。

在任何一致的 ACE 系统中,启用 WriteUnique/WriteLineUnique (WU/WLU) 传输事务后,如果在有一项或多项高速缓存逐出事务处于暂挂状态时尝试执行存储,那么写回无分配 (WBNA) 存储可能发生停滞。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件

Arm Cortex-R5F 处理器包含 1 个 4 输入存储缓冲器,用于对数据先进行缓冲、合并和转发,然后再使用 AXI 主接口将数据写入高速缓存或 L2 存储器系统。由于此错误,存储缓冲器可能进入所有现有写入都无法继续执行的状态。此状态可能会导致下列问题:

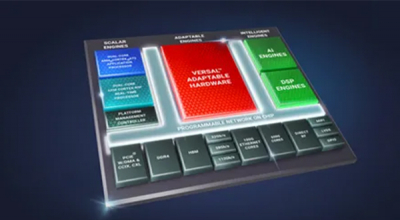

随着AI、大数据、云计算等技术在各行各业广泛应用,相应的设计结构和设计内容也变得日益复杂。目前的应用开发速度已无法满足企业的需求,如何简化设计进程,提高应用开发效率成为当下亟需解决的问题。

在某些条件下,新负载如果复用旧器件负载的分组标识 (GID),则可能报告同步外部异常中止,原因是错误关联旧器件存储器访问所检测到的外部错误。器件负载快速解析完成,并允许后续指令执行时复用 GID。

Arm 发行的白皮书 "Cache Speculation Side-channels"用于发现 "Spectre" 辅助通道。 白皮书指出,DSB SYS 和 ISB 的组合可防止随后的猜测。但是,对于在 DSB SYS + ISB 之后执行页面转换的单次加载、存储或其他内存操作,可推测在 DSB SYS + ISB 完成之前的初始查找中是否发生了 TLB 错误,并填充新的 TLB 条目。

如果用户设计在可编程逻辑中明确强制使用数据 IMUX 寄存器,那么逻辑函数可能不正确。IMUX 寄存器旨在用于进行 Vivado 自动时序最优化。Vivado 设计工具会在时序最优化期间对 IMUX 寄存器进行相应管理,以避免发生此错误。

本文描述Versal™设备中可用的SelectIO™资源。

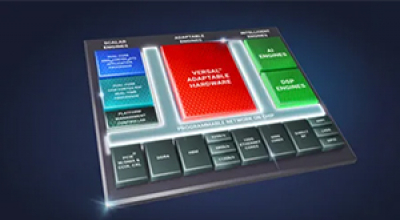

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。

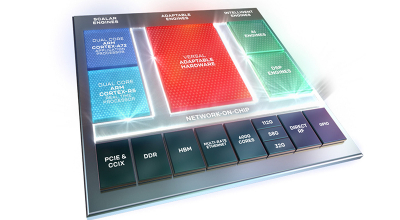

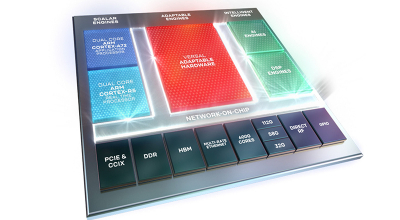

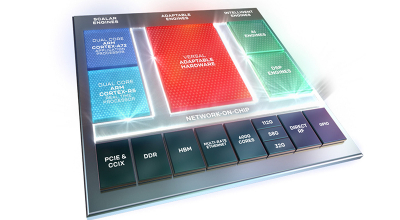

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。