zcu102(8)AXI_STREAM实现AXI_DMA

demi 在 周三, 09/18/2019 - 13:58 提交

AXI_STREAM的时序:AXI_STREAM接口一般用于大规模持续的无地址映射关系的流数据传输......

AXI_STREAM的时序:AXI_STREAM接口一般用于大规模持续的无地址映射关系的流数据传输......

从本文档开始将介绍PS和PL之间通过AXI总线互联。三种AXI总线协议为① AXI_LITE:性能较低的地址映射传输,一次只能传输4字节;② AXI_STREAM:高速流数据传输,无地址映射,不能直接与PS连接;③ AXI(又称AXI_FULL):性能较高的地址映射传输。

axi_timer模块即为PS可以访问的PL计数器,通过计数值以及接入axi_timer的计数时钟周期,可以在PS内取得比较精确的计时。axi_timer有2种使用方式,一种是作为计数器使用,另一种是作为定时器使用。

axi_timer模块即为PS可以访问的PL计数器,通过计数值以及接入axi_timer的计数时钟周期,可以在PS内取得比较精确的计时。axi_timer有2种使用方式,一种是作为计数器使用,另一种是作为定时器使用

PS模块通过axi_bram模块,可以使用AXI接口读写PL内的Block RAM,实现PS与PL之间的数据互联。axi_bram需要与Block Memory Generator模块共同使用,axi_bram将PS的AXI操作转化为bram的控制接口时序。建立Vivado工程,并且添加Zynq模块,AXI BRAM Controller模块,Block Memory Generator模块,Utility Vector Logic模块和ILA模块。

AXI GPIO模块将PL端连接的GPIO信号通过AXI接口与PS模块连接,PS通过AXI接口的地址映射对PL端的GPIO信号进行读写等控制。与EMIO可以实现相同的功能,区别主要在于EMIO对于少数GPIO接口进行单独的控制,而AXI GPIO可以对多个GPIO接口合并成的总线进行整体读写控制。

根据Zynq MPSOC的设计,EMIO占用GPIO BANK3至5的全部32位,对应GPIO的序号78至174,共96个EMIO但是在PS模块中引出的PL中断会默认占用高序号值的EMIO,如本实验中PS模块的pl_resetn0复位信号占用了序号174的EMIO

本文档继承zcu102_1建立的工程,打开Vivado工程后,打开Block Design,双击zynq模块进入配置界面。在PS UltraScale+ Block Design页可以看到UART0和UART1已使能。

本文首先说明了PL开发的完整流程,再对仿真和调试功能进行单独说明。

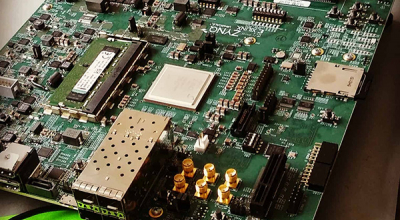

ZCU102 评估套件可帮助设计人员快速启动面向汽车、工业、视频以及通信应用的设计。该套件具有基于 Xilinx 16nm FinFET+ 可编程逻辑架构的 Zynq UltraScale+™ MPSoC 器件,拥有四核 ARM® Cortex-A53、双核 Cortex-R5 实时处理器以及 Mali-400 MP2 图像处理单元。ZCU102 支持所有可实现各种应用开发的主要外设及接口。