面向Abstract shell的DFX

judy 在 周二, 11/30/2021 - 14:57 提交

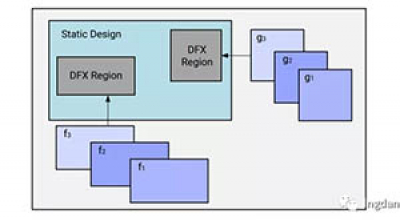

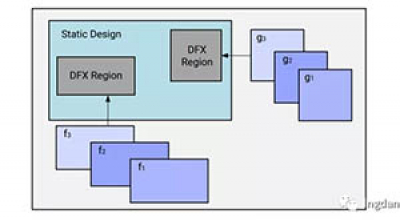

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

Vivado是赛灵思(Xilinx)公司推出的一款集成开发环境(IDE),用于设计和开发基于FPGA(可编程逻辑器件)的数字电路。Vivado提供了一个全面的工具套件,支持从设计到验证、实现和编程的全过程。

Vivado是一种全面的FPGA设计工具,适用于各种应用,包括通信、图像处理、数字信号处理、网络加速和嵌入式系统设计。

使用 DFX 有助于设计者转而采用更少或更小的器件,降低功耗并提高系统升级能力。随时按需加载功能,更有效利用芯片。

本指南详细介绍Vivado®工具中Tcl脚本的使用,查询和修改内存设计的自定义流程。讨论了使用Tcl程序来定义和共享自定义命令。

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

赛灵思亚太区资深战略应用工程师高亚军将为大家讲解Vivado设计套件,分享其在使用过程中的技巧和设计方法论。

2021.2 的新增功能:全新器件支持:Artix® UltraScale+™: XCAU20P 和 XCAU25P;改进的智能设计运行以实现按钮时序收敛;Vivado® 中提供了全新的示例设计;增强高层次综合流的易用性

如何在 Vivado Design Suite 中定义 Verilog Macro?

长期以来,EDA 面临着各种挑战:器件数量越来越多、设计越来越复杂。尽管摩尔定律逐步放缓,但在过去 20 多年间,FPGA 晶体管数量呈现的指数级增长丝毫未减。赛灵思利用堆叠硅片互联等技术,在异构集成方面取得了领先地位,同时还增加了 ARM 处理器子系统、AI 引擎或众多连接块

本文描述了两个ML建模应用,用于提高Vivado® ML版中时序延迟和路由拥塞估计的准确性。

如果 Xilinx USB/Digilent 线缆驱动器在安装 Vivado 设计套件时还没有安装,或者 Xilinx USB/Digilent 线缆驱动器被禁用,在不全面重新安装 Vivado 的情况下,是否能够重新安装该驱动器?

Vivado 仿真器支持混合语言项目文件及混合语言仿真。 这有助于您在 VHDL 设计中包含 Verilog 模块,反过来也是一样。 本文主要介绍使用 Vivado 仿真器进行混合语言仿真的一些要点。