Versal AI Core 系列可借助 AI 引擎提供突破性的 AI 推断加速。此系列应用范围广泛,包括用于云端动态工作负载以及超高带宽网络,同时还可提供高级安全性功能。AI 和数据科学 家以及软硬件开发者均可充分利用高计算密度的优势来加速提升任何应用的性能。

AI 引擎是超长指令字 (VLIW) 处理器阵列,具有高度优化的单指令流多数据流 (SIMD) 矢量单元,专用于各种计算密集 型应用,尤其是数字信号处理 (DSP)、5G 无线应用和人工智能 (AI) 技术(如机器学习 (ML))等。同时,AI 引擎还是硬化的块,可提供多级并行处理能力,包括指令级并行处理和数据级并行处理。

本指南阐述了对 AI 引擎 graph 应用进行编译与仿真、使用 Vitis 工具流程来集成应用、使用 Vitis IDE、调试 AI 引擎应用、映射器/布线器方法论、AI 引擎硬件剖析和调试方法论等内容。

本文选取 AI 引擎架构概述部分。如果您需要获取完整版用户指南,请至文末进行下载。

AI 引擎阵列编程要求充分理解要实现的算法、AI 引擎的功能以及各功能单元之间的整体数据流。AI 引擎阵列支持三种 级别的并行度:

SIMD:通过矢量寄存器,允许并行计算多个元素。

指令级别:通过 VLIW 架构,允许在单个时钟周期内执行多项指令。

多核:通过 AI 引擎阵列,即可在其中并行执行数百个 AI 引擎。

虽然对于 AI 引擎而言,大部分标准 C 语言代码均可编译,但代码可能需要大幅重构才能在 AI 引擎阵列上实现最优性能。AI 引擎的优势在于,它能够在每个时钟周期内执行矢量 MAC 运算、为下一项运算加载 2 个 256 位矢量、存储来自上一项运算的单个 256 位矢量并递增一个指针或执行另一次标量运算。AI 引擎编译器不会执行任何自动矢量化或基于编译指示的矢量化。代码必须重写后才能使用 SIMD 内部数据类型(例如,v8int32)和矢量内部函数(例如, mac(…)),而这些都必须在单个流水打拍循环内执行,才能达成最优性能。32 位标量 RISC 处理器具有一个 ALU、 部分非线性函数和数据类型转换。每个 AI 引擎所能访问的存储器量是有限的,这表示大型数据集需要分区。

AI 引擎内核即 AI 引擎上运行的函数,这些函数构成数据流 graph 规范的基本构建块。数据流 graph 是 Kahn 进程网络,具有确定性行为,不依赖于各种计算延迟或通信延迟。AI 引擎内核声明为空的 C/C++ 函数,通过提取窗口实参或串流实参来建立 graph 连接。内核还可包含静态数据和运行时参数实参,包括异步实参或触发实参。每个内核都应在其自己的源文件内定义。

为了达成总体系统性能,必须广泛阅读了解有关架构、分区、AI 引擎数据流 graph 生成和数据流连接最优化等方面的 知识,积累相关经验。

AMD 赛灵思提供了 DSP 和通信库,其中包含经最优化的代码,可用于 AI 引擎,应尽可能多加利用。其中提供的源代码也提供了强大的资源,供用户学习有关 AI 引擎内核编码的信息。

AI 引擎组件

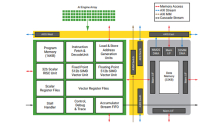

AI 引擎阵列由二维 AI 引擎拼块 (tile) 阵列构成,其中每个 AI 引擎拼块均包含一个 AI 引擎、存储器模块和拼块互连模 块。

AI 引擎:每个 AI 引擎都是一个超长指令字 (VLIW) 处理器,其中包含一个标量单元、一个矢量单元、两个加载单元和一个存储单元。

AI 引擎拼块:每个 AI 引擎拼块都包含一个 AI 引擎、一个本地存储器模块,搭配多条通信路径以促进拼块间的数据交换。

AI 引擎阵列:AI 引擎阵列是指 AI 引擎拼块的完整二维阵列。

AI 引擎程序:AI 引擎程序包含以 C/C++ 编写的数据流 graph 规范。该程序是使用 AI 引擎工具链来编译并执行的。

AI 引擎内核:内核是使用 AI 引擎矢量数据类型和内部函数以 C/C++ 编写的。这些函数均为 AI 引擎上运行的计算函数。内核构成数据流 graph 规范的基本构建块。

ADF graph:ADF graph 是具有单个 AI 引擎内核或多个 AI 引擎内核(以数据串流连接)的网络。它凭借如下特定构造来与可编程逻辑、全局存储器和处理器系统进行交互,此类构造有:PLIO(graph 编程中的端口属性,用于建立往来可编程逻辑的串流连接)、GMIO(graph 编程中的端口属性,用于建立往来全局存储器的外部存储器映射连接)和 RTP。

工具

Vitis 集成设计环境

Vitis™ 集成设计环境 (IDE) 可用于为赛灵思器件执行系统编程,包括含多个 AI 引擎内核的 Versal® 器件。在此工具中,有下列功能特性可用。

最优化 C/C++ 编译器,用于编译内核与 graph 代码,执行所有必要的连接、布局和检查以确保器件上的各项功能正常工作。

周期近似的仿真器、加速的功能仿真器和剖析工具。

调试环境,可在仿真环境和硬件环境下使用。

Vitis 命令行工具

命令行工具可用于构建、仿真以及生成输出文件和报告。捕获由 IDE 生成的命令行输出后,有助于后续集成到客户构建环境内。Vitis 分析器 IDE 可用于查看报告并分析由命令行工具生成的输出文件和报告。

Vitis Model Composer

Vitis™ Model Composer 可提供基于 MATLAB® 和 Simulink® 的高层次图形输入环境,用于包含 AI 引擎、HLS 和 RTL 组件的设计仿真与代码生成。

将 AI 引擎内核、graph、HLS 内核与基于 RTL 的块导入同一个 Simulink® 设计,用于快速协同仿真。

从 Simulink 库浏览器中,将经过最优化的 AI 引擎函数(例如,有限脉冲响应 (FIR) 和 FFT 滤波器)拖放到设计中。

使用 MATLAB 或 Simulink 中生成的激励来验证设计、直观显示结果并将结果与黄金参考结果进行比较。生成 graph 代码并测试矢量。

汇编导入的代码和块库代码以供馈送到下游工具中。

扫码或点击获取完整版《AI 引擎工具和流程用户指南(UG1076)》