仿真是在软件环境内对真实的设计行为进行仿真的进程。仿真有助于通过注入激励并观察设计输出来验证设计的功能。本章提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述。 仿真进程包括:

• 为仿真创建测试激励文件、设置库并指定仿真设置

• 生成网表(如果执行综合后或实现后仿真)

• 使用 Vivado 仿真器或第三方仿真器运行仿真。

文档涵盖了以下设计进程:硬件、IP 和平台开发:为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 Vivado 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。本文档中适用于此设计进程的主题包括:

• 第 3 章:使用第三方仿真器进行仿真

• 第 4 章:使用 Vivado 仿真器进行仿真

• 附录 F: Vivado IDE 中的 SystemC 支持

由于篇幅有限,本文仅节选部分文档内容。如果您希望获取完整版用户指南《Vivado Design Suite 用户指南:逻辑仿真》,请至文末处扫描二维码进行下载。

1. 仿真流程

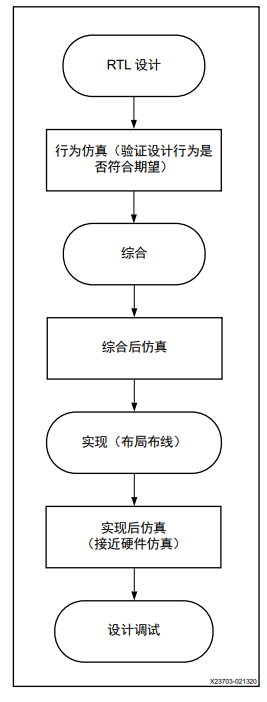

可在设计流程中的多个时间点应用仿真。它是设计输入后的首个步骤之一,也是实现后的最后步骤之一,在验证设计的最终功能和性能过程中执行。

仿真是迭代进程,通常会重复执行直至设计功能和时序要求都得到满足为止。

下图显示了典型设计的仿真流程:

2. 寄存器传输级的行为仿真

寄存器传输级 (RTL) 行为仿真可包括:

RTL 代码

例化的 UNISIM 库组件

例化的 UNIMACRO 组件

UNISIM 门级模型(适用于 Vivado Logic Analyzer)

SECUREIP 库

RTL 级仿真允许您先对自己的设计进行仿真和验证,而后再由综合或实现工具执行任何转换。您可将自己的设计作为模块或实体、块、器件或者系统来进行验证。

通常,执行 RTL 仿真是为了验证代码语法和确认代码功能符合期望。在此步骤中,设计主要以 RTL 来描述,故此无需时序信息。

除非设计包含已例化的器件库组件,否则 RTL 仿真并非局限于特定架构。为支持例化,AMD提供了 UNISIM 库。

通过行为 RTL 来验证设计即可尽早修复设计问题并节省设计周期。

将初始设计创建局限于行为代码即可得到:

更多可读代码

更快且更简单的仿真

代码可移植性(移植到其它器件系列的能力)

代码复用(在未来设计中使用相同代码的能力)

3. 综合后仿真

您可对已综合的网表进行仿真,验证已综合的设计是否满足功能要求并且行为与期望相符。在此仿真时间点,您可以采用估算的时序数值来执行时序仿真,但这并非典型操作。

功能仿真网表是分层折叠网表,它扩展至原语模块和实体级别,其层级的最低层次由原语和宏原语组成。

这些原语包含在 UNISIMS_VER 库(对应 Verilog)和 UNISIM 库(对应 VHDL)内。

4. 实现后仿真

您可在实现后执行功能仿真或时序仿真。时序仿真是最接近实际将设计下载到器件的仿真。它允许您确保已实现的设计满足功能要求和时序要求,并且在器件内的行为与期望的行为相符。

重要提示!执行完整的时序仿真可确保已完成的设计不含任何以其它方式可能无法发现的缺陷,例如:

由于下列原因导致的综合后和实现后功能更改:

造成不匹配问题的综合属性或约束(例如,full_case 和 parallel_case)

设计约束( XDC )文件中应用的 UNISIM 属性

仿真期间由不同仿真器对语言进行的解释

双端口 RAM 冲突

缺失时序约束或者错误应用时序约束

异步路径的操作

由于最优化技巧而引发的功能问题

文档导航

第 1 章:概述

第 2 章:准备仿真 – 本章描述了在 Vivado 集成设计环境( IDE )内仿真 AMD 器件时需要的组件。

第 3 章:使用第三方仿真器进行仿真 – 本章描述了要使用第三方工具执行仿真,可直接在 Vivado 集成设计环境内执行,或者也可以使用定制外部仿真环境来执行。

第 4 章:使用 Vivado 仿真器进行仿真 – 本章描述了 Vivado 仿真器作为硬件描述语言( HDL )事件驱动型仿真器,支持为 VHDL、Verilog、SystemVerilog (SV )及混合 VHDL/Verilog 或 VHDL/SV 设计提供功能仿真和时序仿真。

第 5 章:使用 Vivado 仿真器对仿真波形进行分析 – 本章描述了在 Vivado 仿真器中,可以使用波形来分析设计和调试代码。

第 6 章:使用 Vivado 仿真器进行设计 – 本章描述了调试方法并包含调试进程中实用的 Tcl 命令。此外还提供了有关使用第三方仿真器进行调试的流程描述。

第 7 章:在 Vivado 仿真器中以批处理模式或脚本模式进行仿真 – 本章描述了命令行编译和仿真进程。

获取完整版用户指南

《Vivado Design Suite 用户指南:逻辑仿真(UG900)》

请点击这里或扫描下方二维码进行下载