作者:Nick Liu,来源:FPGA FAE技术分享选集微信公众号

一、Nand Flash接口定义解析

Nand Flash因其具有容量大、成本低、寿命长的特点,被广泛的用作数据存储的解决方案。然而Nand Flash的读写控制较为复杂,Nand Flash的接口控制器大多是基于PC机或ARM处理器为架构进行开发的,存在操作不方便的问题。

FPGA实现Nand Flash接口的优点有很多。首先,FPGA可以实现Nand Flash的高速读写,因为FPGA可以通过并行处理来提高数据传输速度。其次,FPGA可以实现Nand Flash的高可靠性,因为FPGA可以通过ECC校验来检测和纠正数据传输中的错误。此外,FPGA可以实现Nand Flash的低功耗,因为FPGA可以通过动态电压调节技术来降低功耗。最后,FPGA可以实现Nand Flash的高灵活性,因为FPGA可以通过重新编程来适应不同的应用场景。

在Nand Flash控制器中,接口的设计直接影响Nand Flash控制器访问存储颗粒的速度。目前业界有两种主流的接口标准ONFI(Open Nand Flash Interface)与Toggle。ONFI是Intel和Micron等公司主导的开放的Nand Flash接口标准,这里主要针对ONFI标准进行描述。

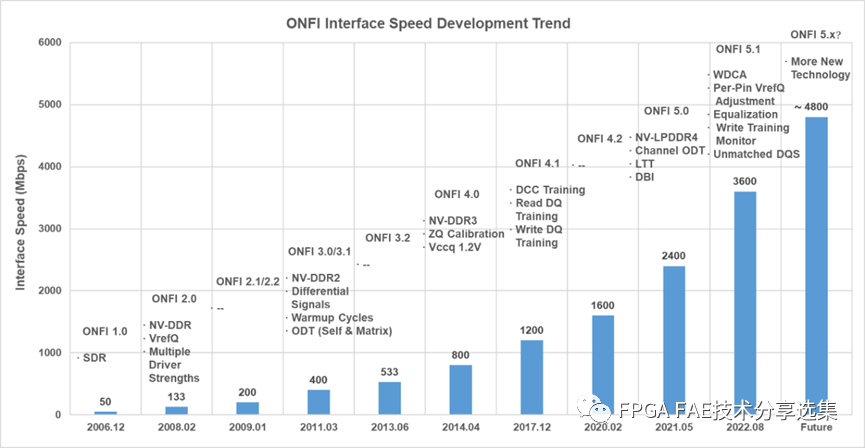

图1、ONFI标准发展

如图1所示,ONFI目前支持5种不同的数据接口类型:SDR/NV-DDR/NV-DDR2/NV-DDR3和NV-LPDDR4。SDR是传统的NAND接口,使用RE_n锁存读数据,WE_n锁存写数据,没有时钟。NV-DDR是双数据率(Double Data Rate-DDR)接口,含有用来锁存命令和地址的时钟,和一个用来锁存数据的数据选通信号。

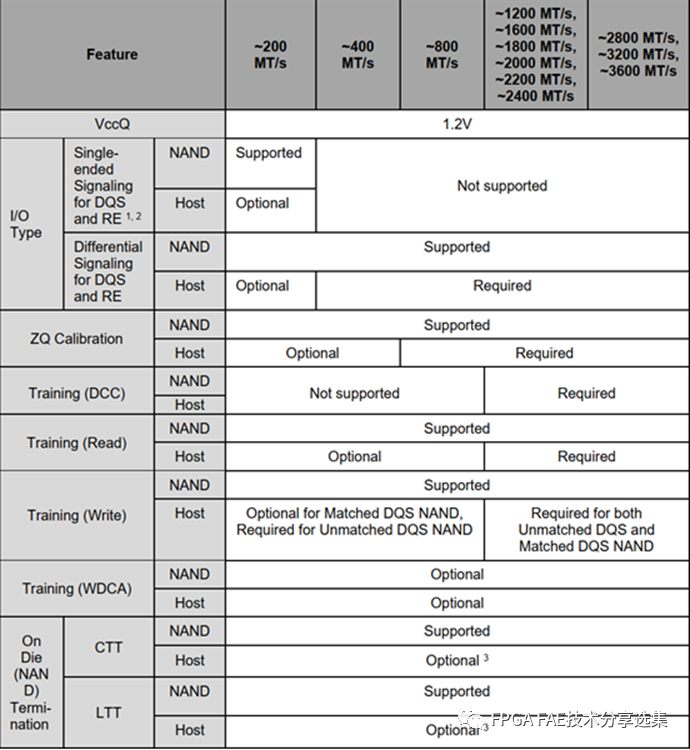

NV-DDR2是双数据率接口,含有额外的扩展速度(scaling speed)的功能,像On-Dietermination以及差分信号。NV-DDR3接口包含所有NV-DDR2的特性,但操作在VccQ=1.2V。数据接口包含的特性如下图2所示。

图2 、ONFI数据接口

如果上电时VccQ=1.8V或3.3V,则device 应该操作在SDR接口timing mode 0。如果 Host 在参数page中判定NV-DDR 和NV-DDR2都被支持,则host可以通过Feature Address为01h的Set Feature命令,来选择其中一个接口以及支持的timing mode。参见ONFI 5.1 5.31.1。

如果上电时VccQ=1.2V,则 device 应操作在NV-DDR3接口timing mode 0。如果host 在参数page中判明了支持的NV-DDR3 timing mode,则host可以通过将CE_n转为高来使能支持的timing mode,并将接口速度改变为期望的timing mode。当host 将CE_n 拉低后,新的timing mode会生效。参见ONFI 5.1\5.31.1。

二、ONFI的接口信号

图4、Signal Assignment based on Data Interface Type

如图4所示,ONFI标准发展过程中的接口SDR/NV-DDR/NV-DDR2/NV-DDR3/NV-LPDDR4,其接口信号也有了相应的调整。

对于NV-DDR/NV-DDR2/NV-DDR3和NV-LPDDR4接口,与 SDR 接口相比,其共同的变化有:

a、I/O总线重命名为DQ总线

b、新加了一个名为DQS(DQ Strobe)的DQ 数据总线选通信号。DQS是双向信号,用于数据传输。DQS不能用于命令或地址周期。对于从host到device的数据传输(写),DQS的锁存沿对齐到有效数据窗口的中间;对于从device到host的数据传输(读),DQS的锁存沿对齐到DQ总线的转换沿。当操作在SDR接口时,DQS应该被host拉高,被device忽略。

对于 NV-DDR 接口,与SDR接口相比,主要变化有:

a、WE_n变成时钟信号(CLK)。CLK应该被使能并且具有有效的时钟周期,不论命令周期,地址周期和数据周期什么时候发生。在CE_n为低期间,CLK应保持相同的频率;参见2.9.1。

b、RE_n变成写/读方向信号(W/R_n)。该信号表示谁拥有DQ总线和DQS信号。Host应该仅在ALE和CLE被锁存到0时才能转换W/R_n;参见4.20.2.6中W/R_n要求。

对于NV-DDR2和NV-DDR3接口,与SDR接口相比,主要变化有:

c、RE_n 可作为单端信号(single-ended)或者作为一个互补信号对(RE_t,RE_c)使用

d、增加了名为DQS(DQ strobe)的DQ数据总线选通信号。DQS可作为单端信号或者作为一个互补信号对(DQS_t,DQS_c)使用。

对于NV-LPDDR4数据接口,与SDR数据接口相比,变化如下:

a、RE_n必须用作互补信号对(RE_t、RE_c)。

b、增加了一个用于DQ数据总线的选通信号,称为DQS(DQ选通)。DQS必须用作互补信号对(DQS_t、DQS_c)。

c、添加了一个用于DQ数据总线的可选数据总线反相信号,称为DBI_n。DBI_ n指定DQ信号是否被反转。DBI_n被视为DQ,因此AC参数和接口训练等规范应适用于DBI。

三、基于AMD FPGA的Nand Flash接口读写实现

基于上述ONFI的协议标准,使用AMD FPGA进行Nand Flash的接口设计有如下几个优点:

由于Nand Flash的接口速率比较高,AMD FPGA的IO口性能通过很多代产品的迭代,IO口性能比较稳定,兼容性较好;

可以使用AMD MPSOC进行设计,通过PS端的程序编写,可以方便地配合PL端进行ONFI标准的接口设计,执行效率高,并且设计比较简单成熟;

在进行ONFI标准升级时,可以通过修改接口PHY部分的硬核逻辑(OSERDES/ISERDES)的配置,就可以提升接口的带宽,可靠性和稳定性都很好。

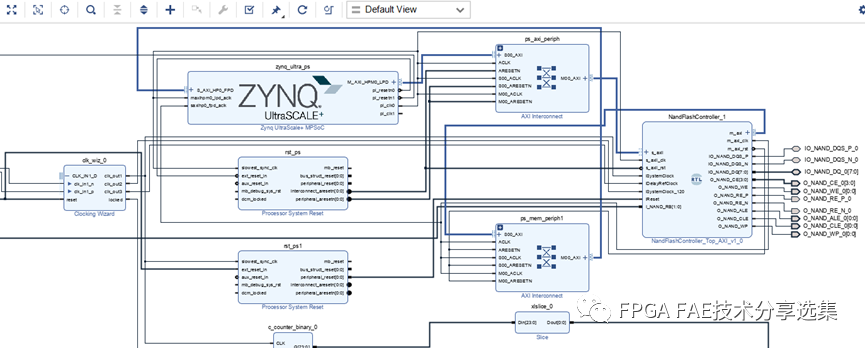

如图5所示,使用AMD 的MPSOC可以方便地通过如下类似的BD配置,只需要PS使用简单函数把Nand Flash当作普通外设即可进行读写,实现数据的配置和读写Nand Flash。如下图所示。图中仅展示了Nand Flash的单个通道的接口BD配置。

由于篇幅有限,不对Nand Flash芯片的各个命令不同模式的时序信号进行介绍,默认大家是了解的。

图5、MPSOC读写Flash的简单BD配置

而其中有关Nand Flash Controller的架构建议如下图6所示。

图6、ONFI的Nand Flash Controller实现

Nand Flash控制器硬件系统中, 各个模块的功能描述如下:

1) 、AXI总线接口模块模块

AXI总线接口模块接收来自PS端或者CPU端发送的命令以及数据信息, 然后把相应的设备状态的值, 通过状态寄存器返回给PS或CPU。它是PS与Nand Flash控制器进行数据、命令等交互的桥梁。

2) 、控制器状态机模块

控制器固件对Nand Flash芯片的各种操作由状态机完成, 状态机包含Nand Flash控制器运行的各种状态, 每一个命令码操作由Nand Flash控制器的各种状态有序组合而成, 共同完成对Nand Flash存储芯片的一次操作。

图7、控制器状态机

Nand Flash控制器的功能实现由控制器状态机模块完成。系统没有操作时, 控制器处于IDLE状态, 命令代码被写入命令寄存器,确定下一步要执行的命令后,Nand Flash控制器转移到某个相应的子状态序列, 完成对存储器的指定操作。

在控制器状态机中, 程序将执行不同功能的控制。每个独立的过程由一个子状态机来实现, 通过系统的时钟来控制所有的状态转换。每个子状态操作完成需要的步骤和时钟个数可能不尽相同, 程序则通过维护一个专用寄存器进行协调, 以确保满足Nand Flash器件的时间控制要求。

3) 、命令接口模块

命令接口用于进行命令的识别和判断,Processor侧可以封装好不同opcode的命令,方便软件进行操作。比如,Select Way0命令,可以设置opcode为6'h20,address为{24'd0,8'b1}。

4) 、数据接口模块

数据接口主要是有关控制器的用户侧数据的输入和输出接口实现(基于AXI接口),比如iWriteData、iWriteLast、iWriteValid、iWriteKeep、WriteReady、oReadData、oReadLast、oReadValid、oReadKeep、iReadReady等。

5) 、缓存模块

缓存模块包括RAM和异步FIFO模块,模块用于缓存命令和数据的双端口RAM,由多个不同RAM和FIFO组成。

6) 、发送引擎模块

根据ONFI的手册,识别Command Interface的不同命令来拼好时隙,保证其通过PHY出去的时候,是符合对应模式下的对应命令的时序的。

7) 、PHY接口模块

PHY接口模块需要使用ISERDES/OSERDES来实现,需要根据用户侧的时钟频率来决定接口的带宽。通常需要向上兼容(为了兼容不同模式下的时序要求),需要兼容老的慢速模式(比如NV-DDR/NV-DDR2等),其信号是上述图中的DQ\DQS\CE\WE等信号。

四、Nand Flash接口功能测试流程和实测结果

对本文所设计实现的Nand Flash控制器的功能, 在EDA软件环境下进行了仿真验证, 其测试流程如图 8所示。

图8、接口测试流程

在图 5所示的仿真验证过程中, 需对Nand Flash芯片进行一系列交互操作, 如读ID、擦除、读设备、页编程、页读取、ECC校验、I/O读等, 且每次操作完成后, 都要读设备状态并判断操作是否成功, 只有操作正常完成才继续进行下一步的操作, 否则退出测试过程。

实际测试的结果是,按照上述方案,已经实现过ONFI2.1(NV-DDR2)的实际测试,暂未进行NV-DDR3接口的实际测试。实测MPSOC使用ZU19EG器件,Nand Flash芯片选用MT29F64G08AECABH1。Nand Flash芯片工作在mode 5状态(8192 Bytes per Page)的实测条件下,实现了48 MB/s的写入速度和93 MB/s 读出速度。

如果您对此文章实现方式有疑问,欢迎联系:

simonyang@comtech.cn

charlesxu@comtech.cn