作者:Yin Chaowen,AMD工程师;来源:AMD开发者社区

1. 关于ILA Cross Trigger

1)ILA Cross Triggering功能使得ILA核心之间、以及ILA核心与处理器(例如,AMD Zynq™ 7000 SoC)之间可以进行Cross Trigger。这个功能在你需要在不同时钟域的两个ILA核心之间触发,或者在处理器和ILA核心之间执行硬件/软件跨触发时非常有用。

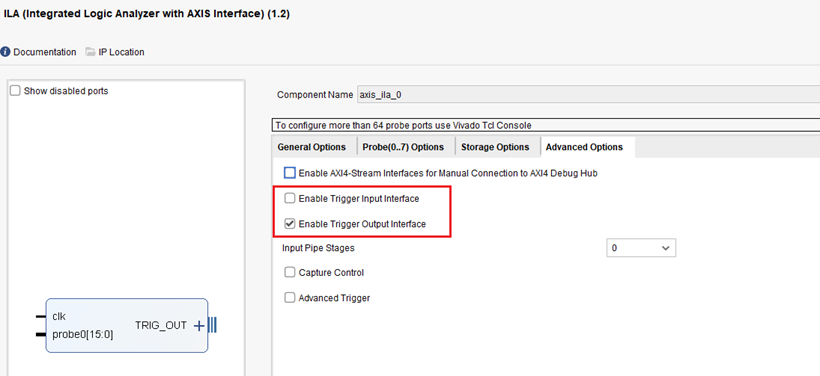

要使用Cross Trigger功能,在核心生成时,你应该配置ILA核心具有专用的触发输入端口(TRIG_IN和TRIG_IN_ACK)和专用的触发输出端口(TRIG_OUT和TRIG_OUT_ACK)。

(一对ILA的TRIG_OUT和TRIG_IN 在Block Design中的互联示意图)

2)RIG_OUT_ACK 信号向 ILA 内核(另一个 ILA、用户设计或处理器)指示 TRIG_OUT 已正确接收,并导致 ILA 在接收 TRIG_OUT_ACK 时降低 TRIG_OUT 信号。

换句话说,TRIG_OUT 保持高电平,直到 TRIG_OUT_ACK 可用。 如果 TRIG_OUT_ACK 信号连接至低电平,则 TRIG_OUT 保持高电平,直到用户重新启动 ILA。 只有 TRIG_OUT 变为低电平。 如果 TRIG_OUT_ACK 连接到低电平,您可以重新准备 ILA。

下图展示了典型的交叉触发设置,其中 ILA2 交叉触发到 ILA1。 ILA2 的 TRIG_OUT 信号连接到 ILA1 的 TRIG_IN 信号。 ILA 1 的 TRIG_IN_ACK 信号连接到 ILA2 的 TRIG_OUT_ACK 信号。

3)典型的交叉触发设置

2. 测试工程基本情况介绍

本测试工程基与Vivado 2022.2

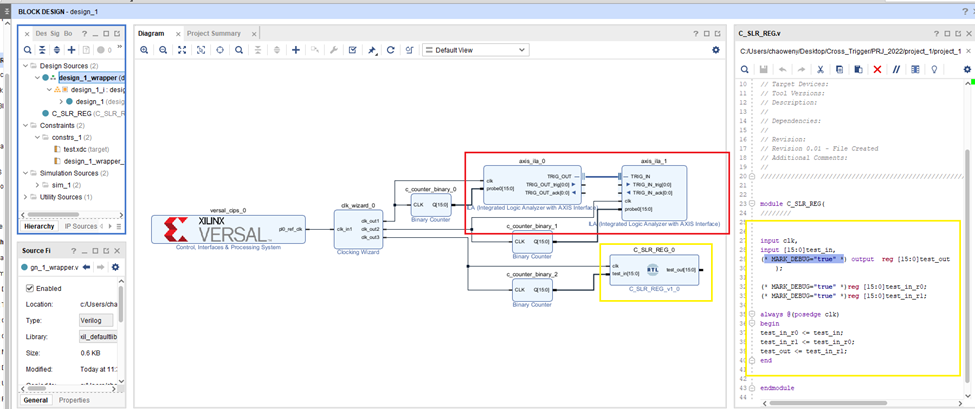

本测试工程基于Versal VCK190 Evaluation Platform (xcvc1902-vsva2197-2MP-e-S),这里同时介绍了以下两种方式实现ILA Cross Trigger:

1. IPI的方式例化带有Cross TRIG端口的ILA。(对应axis_ila_0和axis_ila_1)

2. (* MARK_DEBUG="true" *)+ Tcl脚本的的方式(这种方式只支持Vivado 2022.1及更高版本)

红色方框内的axis_ila_0和axis_ila_1在配置IP的时候直接例化了对应的Cross Trigger接口,黄色方框内是对部分的RTL代码设置了(* MARK_DEBUG="true" *)。

3. 构建步骤

测试的C_SLR_REG module的代码如下:

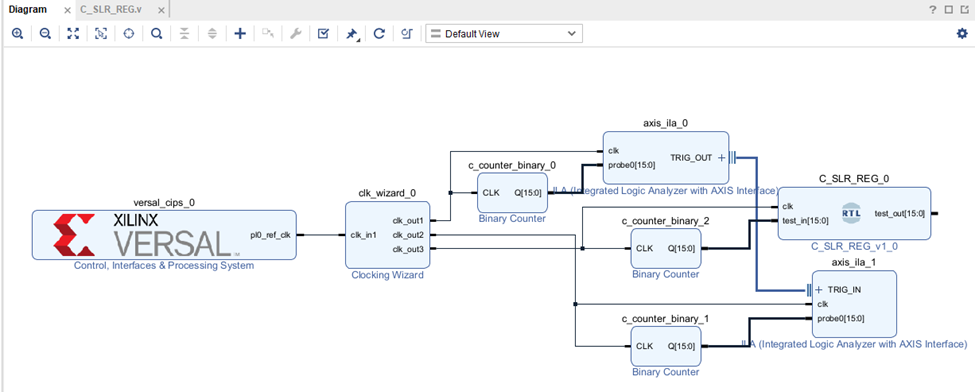

1) 按照下图构建BD工程。

2) 将C_SLR_REG module以RTL的方式加入到BD内, 操作方法见下图。

3) 连接好整个BD然后Create HDL Wrapper并将design_1_wrapper. v设置成top。

4) Run Synthesis

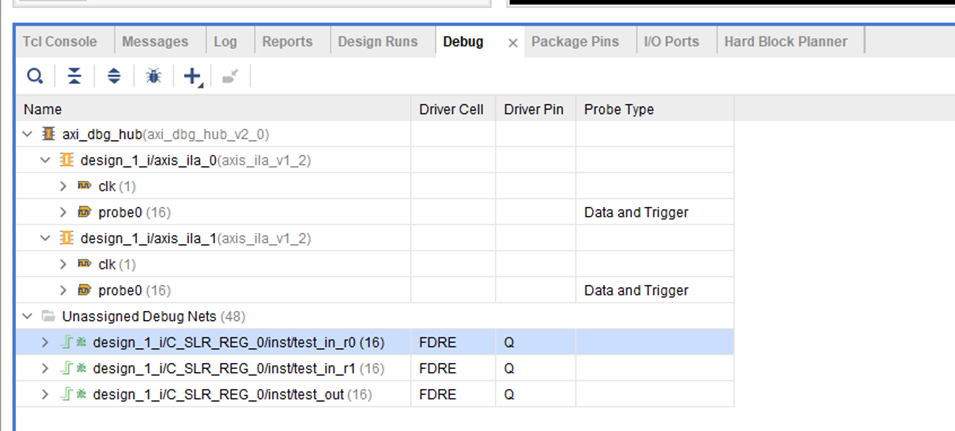

a. 综合完成之后点击Open Synthesized Design

b. 使用如下方式打开Debug窗口

从Debug视图可以看到已有两个IPI例化的ILA(axis_ila_0和axis_ila_1),还有一些Unassigned Debug Nets(

design_1_i/C_SLR_REG_0/inst/test_out,

design_1_i/C_SLR_REG_0/inst/test_in_r0,design_1_i/C_SLR_REG_0/inst/test_in_r1),

下面需要通过Tcl 脚本的方式创建新的debug core将Unassigned Debug Nets连接到新的debug core上。

c. Tcl 脚本创建两个新的debug core(u_ila_2和u_ila_3),(u_ila_3) trig_out -> (u_ila_2) trig_in.

新建一个Tcl脚本(此处位Cross_ila.tcl)。然后在下图位置调用Cross_ila.tcl脚本。

Cross_ila.tcl文件内容如下:

### create u_ila_2

create_debug_core u_ila_2 ila

set_property C_TRIGIN_EN true [get_debug_cores u_ila_2]

set_property C_TRIGOUT_EN false [get_debug_cores u_ila_2]

set_property C_NUM_OF_PROBES 1 [get_debug_cores u_ila_2]

# create u_ila_2 TRIG_IN_trig and TRIG_IN_ack

create_debug_port u_ila_2 TRIG_IN_trig

create_debug_port u_ila_2 TRIG_IN_ack

#config u_ila_2/clk

set_property port_width 1 [get_debug_ports u_ila_2/clk]

connect_debug_port u_ila_2/clk [get_nets [list design_1_i/clk_wizard_0_clk_out3]]

#config u_ila_2/probe0

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_2/probe0]

set_property port_width 16 [get_debug_ports u_ila_2/probe0]

connect_debug_port u_ila_2/probe0 [get_nets [list design_1_i/C_SLR_REG_0/inst/test_out[*]]]

### create u_ila_3

create_debug_core u_ila_3 ila

set_property C_TRIGIN_EN false [get_debug_cores u_ila_3]

set_property C_TRIGOUT_EN true [get_debug_cores u_ila_3]

set_property C_NUM_OF_PROBES 2 [get_debug_cores u_ila_3]

# create u_ila_3 TRIG_IN_trig and TRIG_IN_ack

create_debug_port u_ila_3 TRIG_OUT_trig

create_debug_port u_ila_3 TRIG_OUT_ack

#config u_ila_3/clk

set_property port_width 1 [get_debug_ports u_ila_3/clk]

connect_debug_port u_ila_3/clk [get_nets [list design_1_i/clk_wizard_0_clk_out3]]

## create_debug_core的时候会自动创建probe0和clk端口

# config u_ila_3/probe 0

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_3/probe0]

set_property port_width 16 [get_debug_ports u_ila_3/probe0]

connect_debug_port u_ila_3/probe0 [get_nets [list design_1_i/C_SLR_REG_0/inst/test_in_r0[*]]]

# config u_ila_3/probe 1

create_debug_port u_ila_3 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_3/probe1]

set_property port_width 16 [get_debug_ports u_ila_3/probe1]

connect_debug_port u_ila_3/probe1 [get_nets [list design_1_i/C_SLR_REG_0/inst/test_in_r1[*]]]

### connect u_ila_2/3

create_net ila2_trig_to_ila3

create_net ila2_ack_to_ila3

connect_net -net ila2_trig_to_ila3 -objects [get_pins u_ila_3/TRIG_OUT_trig]

connect_net -net ila2_ack_to_ila3 -objects [get_pins u_ila_3/TRIG_OUT_ack]

connect_net -net ila2_trig_to_ila3 -objects [get_pins u_ila_2/TRIG_IN_trig]

connect_net -net ila2_ack_to_ila3 -objects [get_pins u_ila_2/TRIG_IN_ack]

# set_false_path

set_false_path -through [get_nets {ila2_trig_to_ila3}]

set_false_path -through [get_nets {ila2_ack_to_ila3}]

5) Run Implementation.

6) Generate Devie Image/Bit.

4. HW调试

Implementation完成之后,连接上板卡。

实际运行结果

1) 将PDI文件下载到器件中。

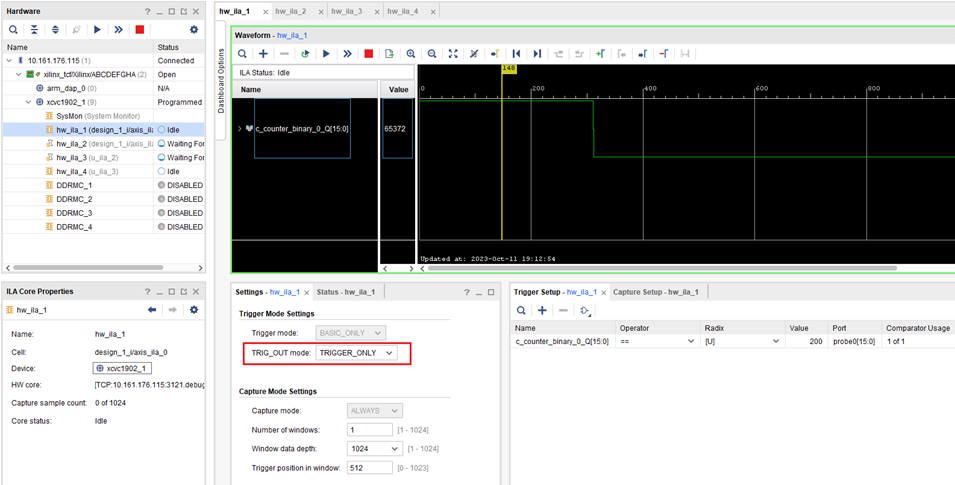

2) 可以发现出现了四个hw_ila_1/2/3/4,与工程中的ila debug core对应关系如下。

hw_ila_1: axis_ila_0

hw_ila_2: axis_ila_1

hw_ila_3: u_ila_2

hw_ila_4: u_ila_3

之前配置的两组Cross Trigger:

axis_ila_0 trig_out -> axis_ila_1 trig_in

(u_ila_3) trig_out -> (u_ila_2) trig_in

即:

hw_ila_1 trig_out -> hw_ila_2 trig_in

hw_ila_4 trig_out -> hw_ila_3 trig_in

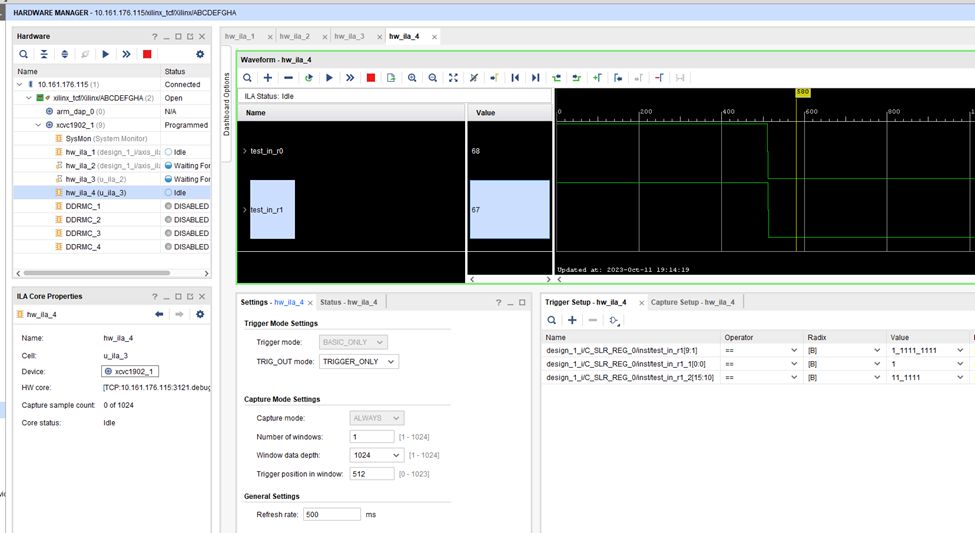

3) 分别设置hw_ila_1/2/3/4的Trigger mode。

(hw_ila_1)

(hw_ila_2)

(hw_ila_3)

(hw_ila_4)

4) 设置完成之后就可以实现ila之间的Cross Trigger.