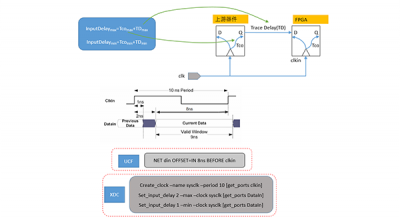

运用 Language Template 来创建set_input_delay/set_output_delay约束

judy 在 周四, 04/08/2021 - 14:37 提交

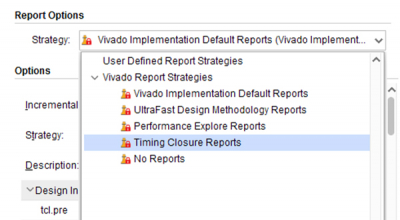

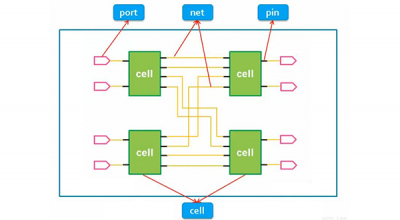

时序约束中的 set_input_delay/set_output_delay 约束一直是一个难点,无论是概念、约束值的计算,还是最终的路径分析,每一次都要费一番脑子。Vivado为方便用户创建输入输出接口的约束,整理出了一套非常实用的InputDelay/Output Delay Constraints Language Templates。