魔视智能与赛灵思战略合作,共同推动自动驾驶系统的量产落地

judy 在 周五, 05/28/2021 - 09:55 提交

魔视智能展示了最新一代遥控泊车(RPA)软硬件一体系统解决方案。该方案采用赛灵思Zu2作为主芯片,能够接4路环视摄像头、12路超声波传感器,遵循ISO26262功能安全开发,符合车规要求。本系统集成了多个神经网络,充分利用芯片优势,解决用户在泊车中的痛点,保证了系统安全可靠。

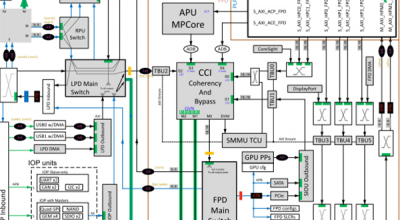

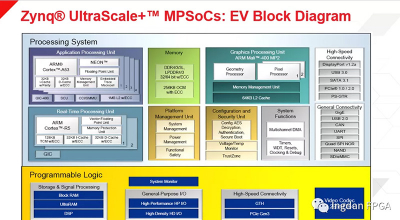

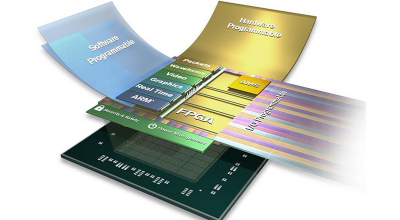

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

魔视智能展示了最新一代遥控泊车(RPA)软硬件一体系统解决方案。该方案采用赛灵思Zu2作为主芯片,能够接4路环视摄像头、12路超声波传感器,遵循ISO26262功能安全开发,符合车规要求。本系统集成了多个神经网络,充分利用芯片优势,解决用户在泊车中的痛点,保证了系统安全可靠。

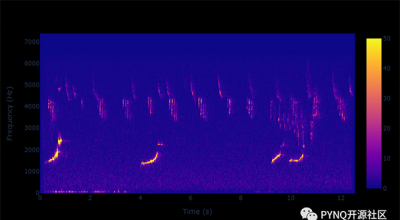

在PYNQ RFSoCWorkshop之后,Xilinx再次推出DSP-PYNQ,与之前只发布了基于RFSoC2x2开发套件的overlay和notebooks不同,本次发布的工程增加了对ZCU111和Ultra96的支持。

OpenAMP framework支持standalone和linux环境下加载RPU的程序,但是没有u-boot下面的支持。U-boot下可以把rpu app binary加载到memory,然后用“cpu”命令启动rpu app。这个流程不是官方支持的方法,所以不在支持范围内,这里只做可行性探讨。下面是简单测试过可行的方法。

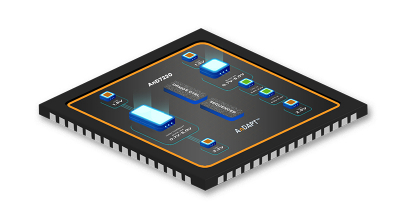

AnDAPT电源解决方案加速对包括工业、电机控制、可编程逻辑控制、物联网(IoT)、医疗、网络和数据中心设备在内的一系列工业和计算应用的供电技术开发。这些即用型参考设计提供了简单可靠的解决方案,在满足所有相关复杂性要求的同时,为整个Xilinx Zynq系列的FPGA/SoC供电。

MPSoC的DDR控制器的数据通道上集成了 AXI performance monitors (APM)。具体情况,可以参考Xilinx UG1085 (v2.2)中Chapter 15的“Figure 15‐1: PS Interconnect”或者Figure 17-1。

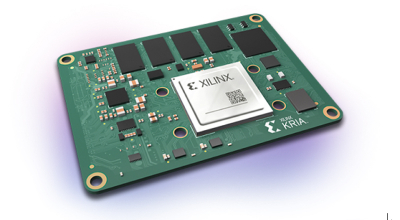

不久以前,从算法到现场机器学习( ML )模型仍然需要经历漫长而复杂的道路。对于一些企业而言,如果能够接触到具有神经网络部署经验的 ML 专家,则可能会有一些选择,但其开发工作却非常耗时。赛灵思依托 Vitis 统一软件平台以及近期推出的 KRIA SOM (System-on-Module),缩短了这一过程。

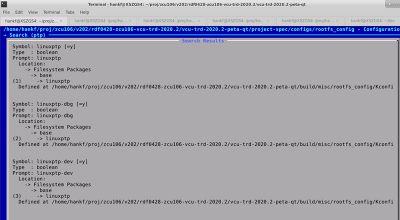

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

在测试MPSoC VCU的编解码时,经常需要使用NV12 YUV文件。YUV文件很大,所以经常依靠解压MP4等文件来产生NV12 YUV文件。 FFMpeg是一个强大的工具,可以用来从MP4文件生成NV12 YUV文件。

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线。比如在文件xfsbl_partition_load.c中,FSBL加载FPGA的bit后会执行下列操作,打开PS和PL之间的接口和信号线