Zynq UltraScale+ MPSoC/RFSoC 设计咨询:在 2019.1 版 XilSecure 中,当数据小于 104 字节时,不支持 SHA3 散列计算

judy 在 周二, 08/25/2020 - 16:54 提交

在 2019.1 版本中,在以下情况下,当数据小于 104 字节时,XilSecure 不支持 SHA3 散列计算:

输入数据处于非字对齐状态

输入数据来自非字对齐地址。

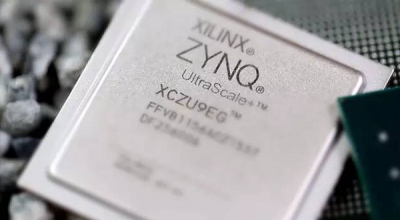

Zynq® UltraScale+™ MPSoC(多处理器系统芯片)是赛灵思(Xilinx)推出的一款集成了处理器系统和可编程逻辑的器件。这一系列芯片采用 UltraScale+ 架构,结合 ARM 处理器和可编程逻辑,为嵌入式系统提供了灵活性和高性能。

Zynq UltraScale+ MPSoC 适用于嵌入式系统设计,特别是对于需要高度定制和硬件加速的应用。它为设计人员提供了处理器和 FPGA 的集成解决方案,以满足各种复杂系统的需求。

在 2019.1 版本中,在以下情况下,当数据小于 104 字节时,XilSecure 不支持 SHA3 散列计算:

输入数据处于非字对齐状态

输入数据来自非字对齐地址。

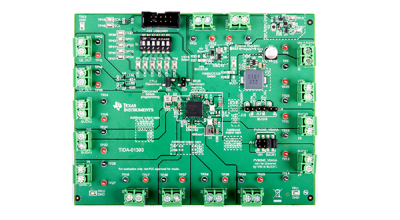

此参考设计是一款可配置电源解决方案,用于在各种用例中对整个 Xilinx® Zynq® UltraScale+ (ZU+) 系列MPSoC 器件进行处理。TPS65086x PMIC 拥有各种版本,因而此设计能够为从具有双核 Arm® Cortex®-A53应用处理器和双核 Arm Cortex-R5 实时处理器的基本ZU2CG 器件到更高端的 ZU7EV、ZU19EG 和ZU21DR 器件供电

在基于供电网络 (PDN) 的共振峰创建的布局前、布局后和系统验证数据模式中分析电源完整性对 FPGA DDR4存储器接口中的信号完整性的影响。使用 FPGA 配置的矢量网络分析仪 (VNA) 测量 PDN 阻抗曲线。创建多个测试数据模式,以便将电源的电流频谱分量与 PDN 共振峰叠加在一起,并演练传输线多次反射累积效应

文档Using Cryptography in Zynq UltraScale MPSoC提供了在Linux用户态使用MPSoC AES 加速器的例子。如果要使用Device key或者PUF key,需要使用Xilinx Linux 2020.1。Xilinx Linux 2020.1增加了选择密钥类型的功能。

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚。

赛灵思今天宣布,搭载赛灵思车规级芯片平台 Zynq® UltraScale+™ MPSoC 的百度 Apollo 自动驾驶计算平台 ACU 于伟创力中国苏州工厂正式量产下线,这款量产的 ACU 硬件平台将率先应用于 Apollo Valet Parking( AVP )自主泊车产品。

米尔科技的FZ3是与百度紧密合作推出的一款基于Xilinx Zynq Ultrascale CZU3EG芯片打造的深度学习计算卡,芯片内部集成了4核ARM A53处理器+GPU+FPGA的架构,具有多核心处理能力、FPGA可编程能能力以及视频流硬件解码能力等特点。

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

本文介绍MPSoC的芯片启动流程

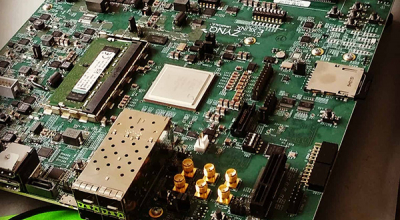

本文展示了通过使用 Design Gateway 的 NVMeG3-IP 内核在 Xilinx 的 ZCU102 评估套件上实现 NVMe 固态硬盘 (SSD) 接口的解决方案,该方案可实现惊人的快速性能:写入速度达 2,319 MB/s,读取速度达 3,347 MB/s。