FPGA设计的几项重要原则

judy 在 周二, 01/04/2022 - 10:08 提交

面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

可能很多FPGA初学者在刚开始学习FPGA设计的时候,经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。

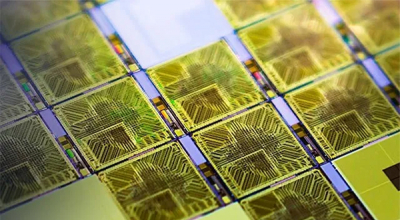

采用核心板模块可以显著降低上市时间和项目风险。基于Xilinx Zynq UltraScale+ MPSoC的Enclustra水星XU5是一个完整而强大的嵌入式处理系统,面积比信用卡还要小。将其插入一个针对特殊应用的底板就可以工作了

领域专家和硬件工程师运用 MATLAB® 和 Simulink® 开发原型和生产应用程序,以部署到 FPGA、ASIC 和 SoC 设备。

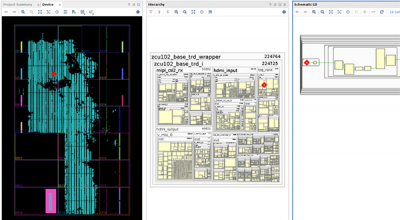

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

FPGA 设计是有章可循的,如果用的是 Xilinx 的 FPGA,这个“章”就是 UG949。最新版的 UG949 是 2020.1 版本,整个文档共六大章节 306 页(点击此处查看《UltraFast 设计方法指南》)。对于如此之多的内容该如何消化吸收呢?首先,了解一下 UG949 的背景信息。

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实

现在的FPGA设计,规模巨大而且功能复杂,因此设计的每一个部分都从头开始是不切实际的。一种解决的办法是:对于较为通用的部分可以重用现有的功能模块,而把主要的时间和资源用在设计中的那些全新的、独特的部分。这就像是你在开发应用程序的时候就不用直接去写驱动物理硬件的代码

今天跟大家分享的内容很重要,也是我们调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码可能无法满足时序要求。

许多 FPGA 设计都难以达成所期望的性能目标。原因不尽相同,以下列出的只是其中部分可能的原因:未遵循 UltraFast 设计方法;时序约束不良;过高资源利用率;控制集过多;未采用最优化时钟设置;逻辑层次过多,难以达成目标性能;布局规划不良;布线拥塞;因约束导致工具优化受限。