XILINX BMG (Block Memory Generator)

joycha 在 周一, 01/04/2021 - 15:21 提交

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

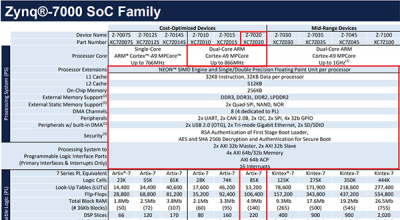

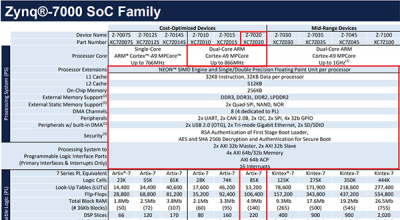

观看 Zynq-7000 安全设计的演示,了解我们独特的功能安全方法。

ZYNQ7000系列FPGA的PS自带两个IIC接口,接口PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);SDK中需要对IIC接口进行初始化在黑金和米联的例程里为了方便用户使用,对IIC和外设设备分别创建了相应的文件方便用户开发。

Zynq-7000和MPSoC有很多MIO管脚。如果外设有中断,也可以通过MIO驱动。

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

随着赛灵思公司推出28nm Zynq-7000 All Programmable SoC以后,FPGA在工业应用大有加速之势,赛灵思工业级客户增长非常迅猛,其数量远超通信客户。赛灵思Zynq器件在智能化工业自动化领域大显身手,它将给工业应用带来哪些深刻变革?

复位系统包括由硬件,看门狗定时器,JTAG控制器和软件产生的复位。Zynq-7000 SoC器件中的每个模块和系统都包含一个由复位系统驱动的复位。硬件复位由上电复位信号(PS_POR_B)和系统复位信号(PS_SRST_B)驱动。

本文演示了使用Vivado®Design Suite和Vitis™软件平台构建基于Zynq®-7000SoC处理器的嵌入式设计。提供有效的嵌入式系统设计教程。

在ZC702单板上,MicroBlaze通过IC/DC端口连接到PS S_AXI_GP0,MicroBlaze读取OCM,得到值DECODE1C。MicroBlaze改为通过DP端口连接到PS S_AXI_GP0,再读取OCM,正常。

作者:付汉杰,hankf@xilinx.com,文章转载自:博客园