作者:杨智勇,本文转载自: Ingdan FPGA微信公众号

在Serdes流行之前,芯片之间的数据传输主要靠低俗串行接口和并行接口(包含源同步接口和异步接口),存在诸如传输速率低、占用IO数量多、硬件连接复杂化等弊端。Serdes的出现简化了数据传输接口的硬件设计,大大提升了数据传输的速率和带宽效率。

Xilinx FPGA自Virtex-2 Pro系列开始集成最高支持2.488Gbps线速率的RockitIO MGT和最高支持6.25Gbps线速率的RockitIO-X MGT,之后的FPGA产品系列中集成的Serdes也在不断演进,到如今在众多用户的量产设计中使用的Ultrascale和Ultrascale+系列FPGA,已经集成了最高支持16.3Gbps线速率的GTH、最高支持32.75Gbps线速率的GTY和最高支持58Gbps线速率的GTM,更是在7nm Versal系列FPGA中集成了最高支持112Gbps线速率的GTM(Combine模式)。

今天我们来聊一聊7 Series、Ultrascale系列GTH与Ultrascale+ GTY的内部区别,Serdes的内部结构和工作原理不在本文中讨论,各种高速串行协议和接口也不在本文中讨论。

我们简单整理了一下主要区别点如下:

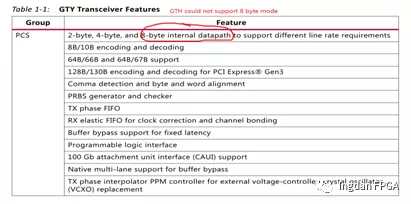

1. 在GTH中留给用户逻辑接口的interface data width最大可以到80bit,但是GTH内部的internal data width最大只能支持到40bit,我们知道Serdes线速率和internal data width、编码方式、txusrclk2/ rxusrclk2是线性比例关系,随着Serdes支持最高线速率的提升,越来越高的txusrclk2/ rxusrclk2时钟频率将会使逻辑时序的收敛成为一个突出的问题,在Ultrascale+ GTY内部支持了最高80bit internal data width,方便用户在时序收敛容易实现的频率做到更高的Serdes线速率;

2. 高速信号在硬件链路中传输时,越来越高的线速率和愈加复杂的应用场景,对于Serdes RX端均衡器的能力要求也相应增加,Ultrascale+ GTY内部支持了15阶可配置为自适应模式的DFE,对于高线速率、高损耗链路的应用场景,接收端均衡能力有着更好的性能;

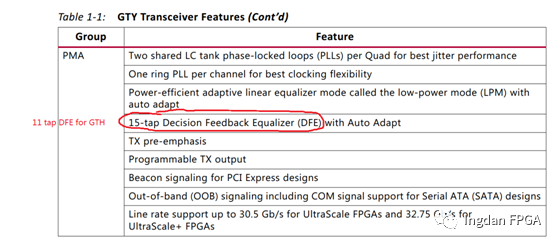

3. 在7 Series的GTH Quad中,在一个GTH Quad内有四个CPLL和一个QPLL,而在Ultrascale的GTH Quad中、Ultrascale+的GTH Quad中、Ultrascale+的GTY Quad中,则变成了四个CPLL和两个QPLL,QPLL具备更好的Jitter性能和更高的频率支持,增加一个QPLL可以更好地应对在一个GTH/GTY Quad内设计多种高速串行协议的应用场景和使用多种线速率的应用场景;

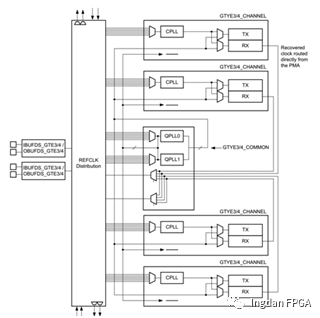

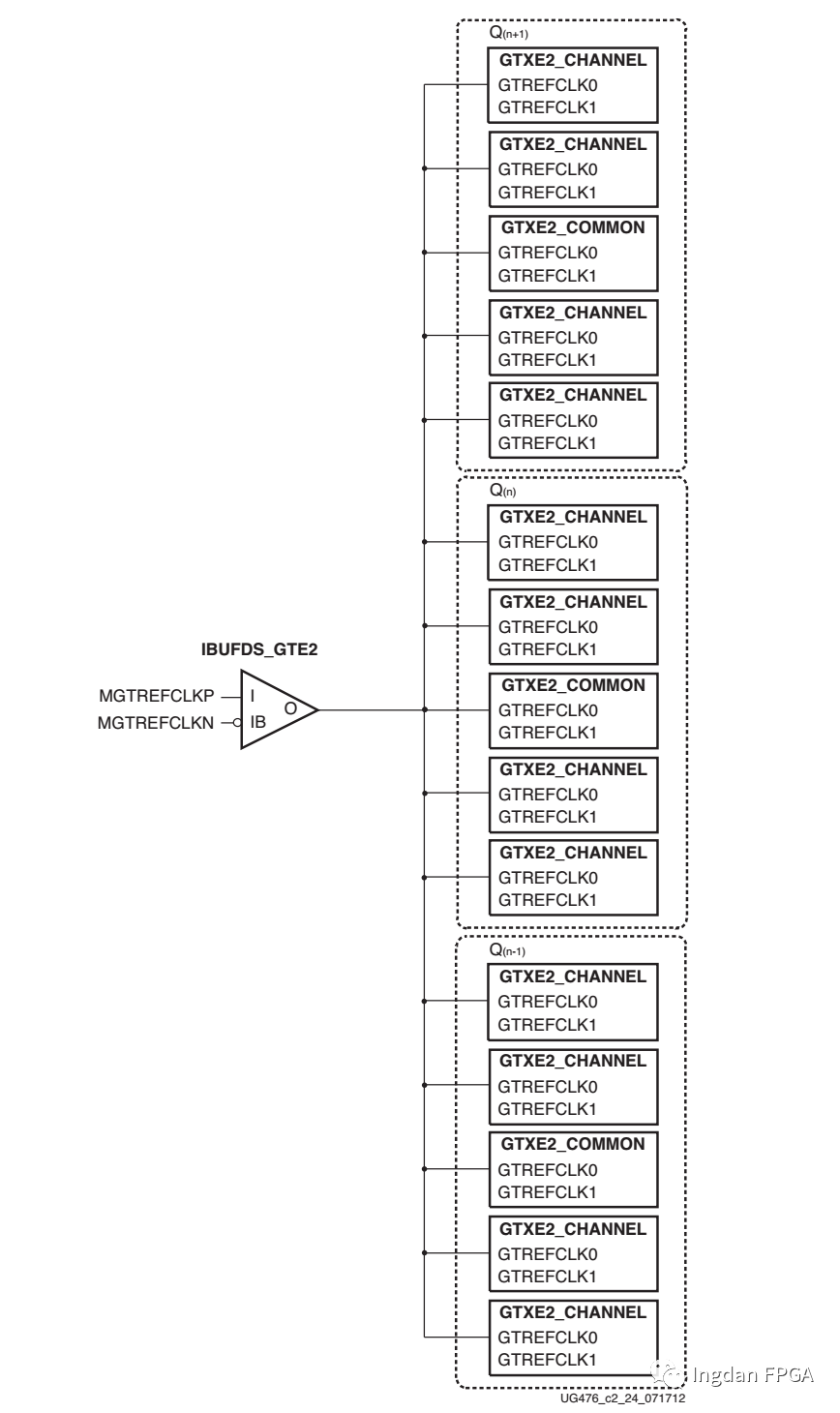

4. 在7 Series的GTX/GTH时,一对参考时钟输入最多可以驱动上下相邻的三个GTX/GTH Quad,共计12个Serdes;而在Ultrascale和Ultrascale+的GTH/GTY时钟结构中,一对参考时钟输入最多可以驱动上下相邻的五个GTH/GTY Quad,这种新的时钟走线结构在Channel Bonding和multi-lane数据对齐的时候会更加方便;

7 Series GTREFCLK驱动范围

Ultrascale & Ultrascale+ GTREFCLK驱动范围

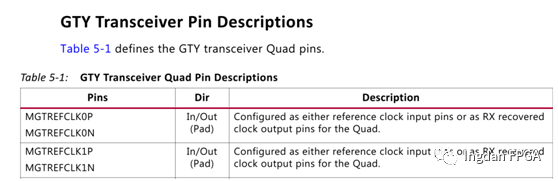

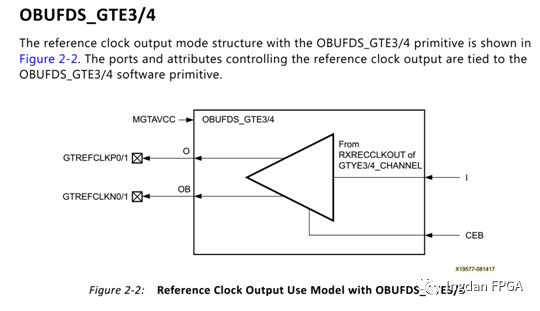

5. 在7 Series的GTX/GTH时,参考时钟输入PIN只可以用作时钟输入,而在Ultrascale的GTH和Ultrascale+的GTH/GTY中,参考时钟输入PIN还可以配置作为本Quad内任一个GTH/GTY的恢复时钟RXRECCLK的输出PIN,此输出时钟可以再作为其他GTH/GTY Quad的参考时钟输入,在某些应用场景下可以简化Serdes的参考时钟网络设计;

6. 在Serdes一些常用调试观测端口的命名上,Ultrascale GTH、Ultrscale+ GTH/GTY与7 Series GTX/GTH有一些变化,信号端口的具体含义对应如下;

如果您在使用中遇到Serdes和各种高速接口相关问题,欢迎与我们联系交流。联系我们:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn