Xilinx 7系列FPGA收发器架构之共享功能(四)

judy 在 周五, 12/09/2022 - 11:33 提交

GTX/GTH收发器在FPGA上电和配置后必须进行初始化,GTX/GTH收发器的发送器和接收器可以独立

GTX/GTH收发器在FPGA上电和配置后必须进行初始化,GTX/GTH收发器的发送器和接收器可以独立

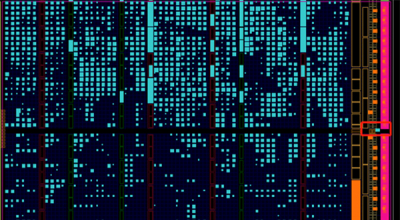

本文主要介绍GTX/GTH收发器内部CPLL和QPLL锁相环时钟结构及使用

本博文主要对GTX/GTH收发器的共享资源进行介绍

本博文主要对GTX/GTH收发器进行总体概述。

将管脚输入的第一个触发器使用ILOGIC来实现有助于每次编译过程中时序的确定性。

本文继续介绍Xilinx 7系列FPGA SelcetIO电平标准及相关端接匹配电路。

AMD 赛灵思很高兴正式宣布,对所有 7 系列 FPGA 和自适应 SoC 的支持将至少延长至 2035 年

本文我们重点介绍一下内容:7系列FPGA DCI使用规则,DCI在HSTL和SSTL I/O标准中的使用举例

通过属性或者约束可以访问7系列FPGA I/O资源某些特性。本文我们介绍和I/O资源相关的属性和约束

这篇文章主要是通过介绍7系列与之前产品的对比,来展示7系列产品的基本逻辑单元的优点。