Vitis Command Line Flow 和 Vitis Analyzer

judy 在 周一, 11/02/2020 - 10:02 提交

该视频在命令行显示了 Vitis 流程的主要设计步骤。 然后显示了如何使用 Vitis Analyzer 以图形方式分析编译结果。

Vitis 是由赛灵思(Xilinx)推出的一款开发工具套件,用于加速应用程序的开发和部署,尤其专注于基于赛灵思的可编程逻辑设备(FPGA)的加速。

Vitis 工具套件的目标是简化 FPGA 加速应用程序的开发流程,使更广泛的开发者能够充分利用 FPGA 提供的硬件加速性能,从而加速特定领域的计算任务。

该视频在命令行显示了 Vitis 流程的主要设计步骤。 然后显示了如何使用 Vitis Analyzer 以图形方式分析编译结果。

在这个直播课程中,我们将为大家详细介绍 Vitis 加速库,讲解库的构成和分类,以及如何在 Vitis 开发环境及 Xilinx 硬件平台上分层应用最适合的 Vitis 加速库。我们还会以 Alveo U50 加速卡为例,选取 Vitis 加速库中的一个压缩算法 Zlib 为例,详细介绍算法的构成、性能,并实例展示如何在 U50 板卡上实现 Vitis Zlib 算法库。

这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis™ 中将所有这些工程封装在一起。

这是《创建 Vitis 加速平台》系列的第 2 篇博文。在前文中,我们讲解了如何创建硬件以及如何通过 XSA 将元数据 (metadata) 传递给 Vitis™。在本文中,我们将讲解如何使用此 XSA 以及如何创建在目标平台上实现设计加速所需的软件镜像。

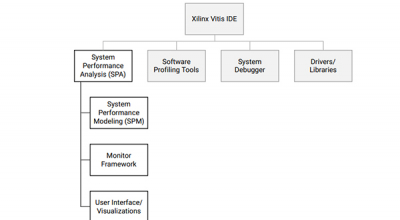

本指南描述了嵌入式设计中的系统性能监控。

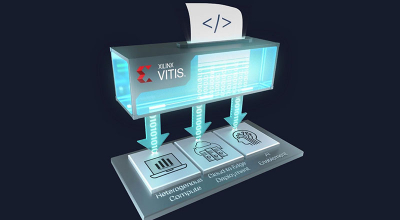

Vitis统一软件平台可以在包括FPGA、SoC和Versal ACAP在内的异构Xilinx平台上开发嵌入式软件和加速应用程序。它为加速边缘计算、云计算和混合计算应用程序提供了统一的编程模型。

在本次网络研讨会上,我们将展示 Vitis 和 Vitis AI 如何帮助开发人员在 Xilinx 平台上加速整个应用。

为了让大家更好的了解Vitis™ / Vitis™ AI统一软件平台和如何使用Vitis™ / Vitis™ AI进行此次比赛设计。本次加速教程邀请到 Adam Taylor 一起了解如何使用Vitis™ 和Vitis™AI 启动设计

在数据处理中,对原始数据进行重塑或重新排序并创建多个副本是很常见的行为。无论执行任何新步骤,都会创建新副本。随着程序的增大,占用的内存也会增大,我几乎从未考虑过这个问题,直到遇到了“内存不足”错误。

本文设计了基于深度学习的人脸口罩佩戴识别系统。该方法在利用自主设计的图像识别网络以及Xilinx最新的vitis-ai技术快速开发出符合要求的系统。利用近1万个公开数据,并采用数据增强等方法,在训练后得到95%的识别准确率