【用户指南】 Vitis AI:加速AI潜能的创新性探索

judy 在 周三, 04/28/2021 - 10:21 提交

随着第三次人工智能浪潮的到来,AI正以前所未有的速度覆盖生产和管理等领域,市场对AI推断的效率与易用性都提出了更高的要求。赛灵思通过 Vitis AI和自适应计算加速平台充分发掘AI 加速潜能并将底层 FPGA 和 ACAP 的繁复细节抽象化,帮助缺乏专业知识的用户轻松开发深度学习推断应用,再度刷新AI推断的高效性和易用性。

Vitis 是由赛灵思(Xilinx)推出的一款开发工具套件,用于加速应用程序的开发和部署,尤其专注于基于赛灵思的可编程逻辑设备(FPGA)的加速。

Vitis 工具套件的目标是简化 FPGA 加速应用程序的开发流程,使更广泛的开发者能够充分利用 FPGA 提供的硬件加速性能,从而加速特定领域的计算任务。

随着第三次人工智能浪潮的到来,AI正以前所未有的速度覆盖生产和管理等领域,市场对AI推断的效率与易用性都提出了更高的要求。赛灵思通过 Vitis AI和自适应计算加速平台充分发掘AI 加速潜能并将底层 FPGA 和 ACAP 的繁复细节抽象化,帮助缺乏专业知识的用户轻松开发深度学习推断应用,再度刷新AI推断的高效性和易用性。

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。

本示例工程中我们会在 TensorFlow2 下使用 Keras API 创建一个自定义 CNN 网络,在 Vitis-AI 1.3 环境下编译成 Xilinx DPU 上运行的模型文件,并在 Xilinx zynqMP 上部署运行。该示例工程应在 Vitis-AI1.3 Docker,vitis-ai-tensorflow2conda 环境中运行。

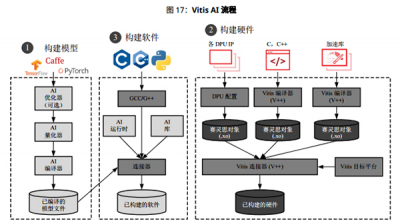

本视频简要介绍了 Vitis AI Edge IP 的计划和架构,包括全新 1.3 版本中的新增功能。

本视频快速介绍 Vitis AI Model Zoo 的计划和内容,包括全新 1.3 版本中的新增功能。

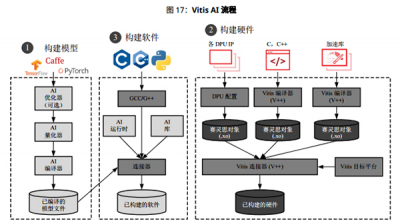

本视频介绍了Vitis和Vitis-AI,将重点讲解Vitis-AI的设计流程以及如何在边缘和云端器件上进行部署。

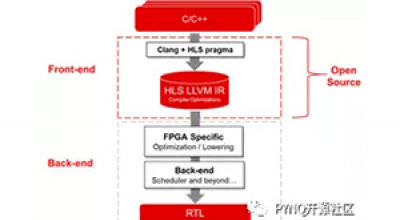

赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端。Vitis HLS 工具能够将 C++ 和 OpenCL™ 功能部署到器件的逻辑结构和 RAM/DSP 块上。

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技术的不断进步,以及算法迭代的日益频繁,人们似乎并不满足于此。

不少刚刚接触到Pynq的用户第一个问号?Pynq是不是用Python编程FPGA的新物种?

去年,赛灵思宣布举办首届自适应计算挑战赛,其中包括开发者和初创企业两项赛事,鼓励其使用 Vitis 统一软件平台和 Vitis AI,在指定赛灵思硬件平台上开发令人振奋的新应用。今年年初,我们公布了开发者竞赛的获胜者。现在,让我们揭晓初创企业竞赛单元的前三甲!他们分别是韩国BLUEDOT、中国雪湖科技以及西班牙Katoid Technology!

由 Ubuntu 16.04 机器上不兼容 GTK 版本导致的 Eclipse GUI 问题