【下载】Bootgen用户指南 (中文版)

judy 在 周三, 06/24/2020 - 17:17 提交

本文档摘自 UG1416 中的“Bootgen 工具”章节,描述了如何为 Zynq®-7000 SoC、7 系列 FPGA 和 Versal™ ACAP 器件生成启动镜像。

本文档摘自 UG1416 中的“Bootgen 工具”章节,描述了如何为 Zynq®-7000 SoC、7 系列 FPGA 和 Versal™ ACAP 器件生成启动镜像。

随着对视频直播的需求不断增长,更快的工作负载成为重中之重。视频服务提供商在控制其基础架构和运营成本的同时,还面临着提供高质量用户体验的挑战。鉴于转换视频的计算密度,转码需要灵活应变的硬件加速平台。

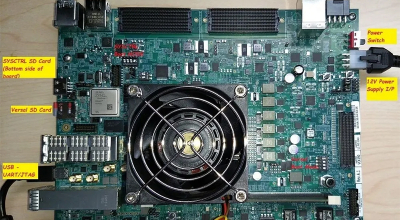

Versal™ ACAP(自适应计算加速平台)是高度集成化的多核计算平台,可通过灵活的自适应能力来满足不断变化的动态算法的需求。VCK190 是赛灵思最早发布的 Versal AI Core 评估器件之一。本篇博文将为您详解如下所述设计创建步骤:

结合 SDSoC 和赛灵思 SDK,SDAccel 流现在是 2019.2 Vitis™ 统一软件平台的组成部分,便于开发者针对赛灵思器件上的所有软件任务使用统一平台。下面分享来自 DesignLinx 公司高级嵌入式软件工程师 Nathan Sullivan 所撰写的技巧

Vivado 2020.1 新增以下功能:

能够将完整的图像或选定的产品作为 Web 安装程序的一部分

增强的地址映射,用于实时错误高亮显示和交叉探测

Report QoR Suggestions 功能可预测多达 3 种自定义策略,以提升性能

嵌套 DFX 为您的 DFX 解决方案提供了更大的灵活性

基于电源通道的报告

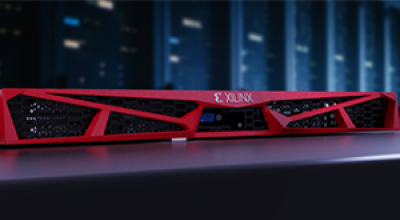

赛灵思今天宣布推出两款易于扩展、超高密度视频转码专用的实时计算视频实时转码一体机。基于赛灵思新型的实时服务器( RT Server )参考架构,两大全新一体机将双管齐下,助力当今服务提供商以每通道最低成本提供视频质量和比特率优化的多种类型应用

现在,企业和专业用户越来越意识到从物理和虚拟世界收集到的大量数据蕴含的价值。随着数据量继续呈指数级增长,对数据分析的需求也将以类似的速度增长。为此,数据中心必须加速转型,以达到增加网络带宽,优化人工智能等工作负载的目的

所谓创造世界记录,就是以某种方式宣告:“这是我们身为人类的最好成绩。现在让我们一起打破它。”从棒球、吉尼斯世界记录到奥运会,人类在举重、跳高、跑步项目上屡屡打破记录。而在商业领域,能够比竞争对手更快地做出响应并快速进行调整,是一件极具价值的事情。

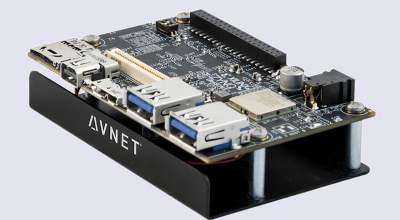

Ultra 96™ 是构建边缘用例机器学习应用的绝佳平台。Zynq® MPSoC ZU3 器件采用的 96 电路板的外形尺寸以及可编程逻辑,使其能够灵活地添加用于此类终端应用视频输入的通用 MIPI CSI2 RX 标准接口。同时为了驱动高性能、低功耗机器学习边缘应用,也可以将赛灵思深度学习处理单元 ( DPU ) 集成到设计中。

本指南为 Zynq-7000 AP SoC、Zynq® Ultrascale+™ MPSoC 和 MicroBlaze™ 器件在 Xilinx® 虚拟仿真平台 (QEMU) 上进行软件开发提供了全面的指导。包括入门和快速参考信息,以及如何调试和创建QEMU启动映像的信息。