【开发必看】一文了解Xilinx 的“全局”

judy 在 周三, 04/29/2020 - 17:53 提交

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手

现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手

有些应用中,单板没有DDR,OCM又不够存储所有数据和指令。这种情况下,Xilinx提供了参考设计Zynq-7000 AP SoC Boot - Booting and Running Without External Memory,把代码和只读数据放在QSPI Flash中运行程序,这就是execute in place (XIP)。

2011年,德国鲁尔大学的两位博士花了3000美元和7个小时成功破解了Mifare DESFire MF3ICD40使用的安全算法,但这个破解在现实生活却没有任何价值,因为一颗RFID芯片的价值只有几分钱,没人傻到去花大钱去破解一个几乎免费的芯片

在本文中,您将了解有关内部集成电路总线(I2C 或 IIC)的基础知识以及将此协议总线应用于短距离通信的方法。I2C 属于串行通信协议,供双线接口用于连接 EEPROM、传感器、RTC、ADC/DAC 等低速器件以及嵌入式系统中的其它兼容 I/O 接口。

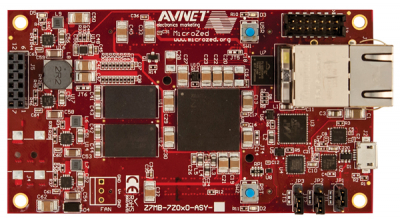

Vitis是Xilinx新推出的统一软件平台,可实现在 Xilinx 所有芯片(包括 FPGA、SoC 和 Versal ACAP)上开发嵌入式软件和加速应用。Xilinx主要宣传Vitis可以为异构平台的应用实现加速。其实,Vitis也能完美的支持嵌入式软件开发。下面以MicroZed单板为例,介绍在Vitis里如何创建嵌入式软件工程,并且编译和调试,直到启动。

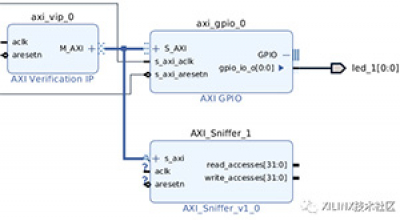

在某些情况下,通过嗅探 AXI 接口来分析其中正在发生的传输事务是很有用的。在本文中,我将为大家演示如何创建基本 AXI4-Lite Sniffer IP 以对特定地址上正在发生的读写传输事务进行计数。首先,编写 HDL (Verilog) 代码,然后将其封装为 IP,最后将此 IP 添加到 IP IntegratorBlock Design (BD) 中。

通过此次研讨会,您将了解 Genetalks 如何借助 Alveo 实现惊人的大数据加速,以及如何借助这一利器为当前的疫情反击和超大数据基因组分析研究与实践提供强大支持

赛灵思今日宣布,三星电子有限公司( Samsung Electronics Co., Ltd. )将采用赛灵思 Versal™ 自适应计算加速平台( ACAP )进行全球 5G 商用部署。赛灵思 Versal ACAP 提供了一个通用、灵活且可扩展的平台,能够满足多地区多运营商的需求。

在 AXI 基础第 2 讲 一文中,曾提到赛灵思 Verification IP (AXI VIP) 可用作为 AXI 协议检查工具。在本次第4讲中,我们将来了解下如何使用它在 AXI4 (Full) 主接口中执行验证(和查找错误)

您可能不太熟悉百度的 DeepSpeech2 自动语音识别(ASR, Automatic Speech Recognition)模型,但我敢打赌,当您正在阅读本文的时候,语音识别其实已经成为您日常生活的一部分,比如 Siri,小爱同学,小度......