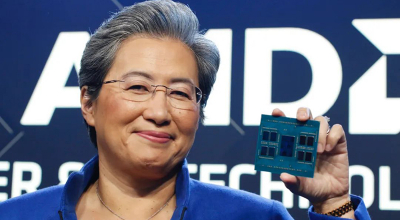

AMD公布2023年第三季度财报

judy 在 周三, 11/01/2023 - 15:06 提交

AMD公布2023年第三季度营业额达58亿美元,毛利率47%

AMD公布2023年第三季度营业额达58亿美元,毛利率47%

第四代 AMD EPYC处理器带来卓越的技术计算性能

在Vitis调试kernel过程中,用户可以在先行通过SW_EMU和HW_EMU测试

如何使用AXI HPC端口进行CCI coherent的高速数据传输呢?

在本文中,我们将聊聊内核

在技术进步的加持下,AV行业发展得如何了?

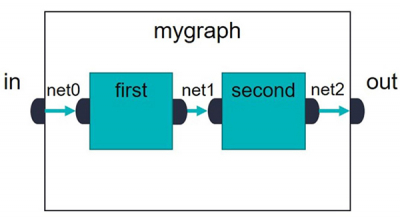

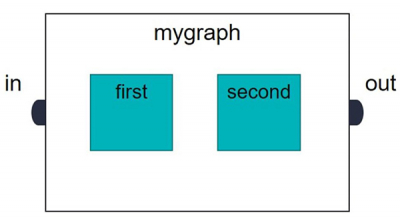

本文将进一步深入讲解工程内的 AIE graph

此次研讨会将全面覆盖AMD在工业、医疗及相关领域的图像最新应用

AMD公布了第四代EPYC家族处理器的一系列更新

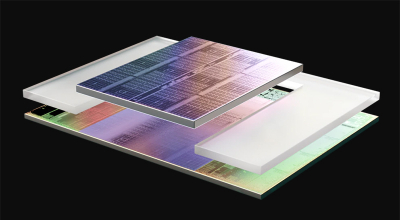

AMD在单个GPU能做到上千T的浮点算力规模