适用于 SSIT 器件的 Versal Fmax 限制

judy 在 周五, 04/14/2023 - 15:34 提交

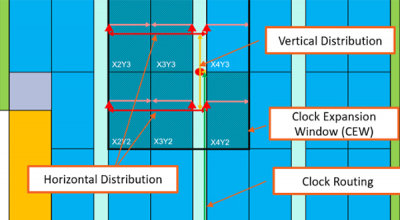

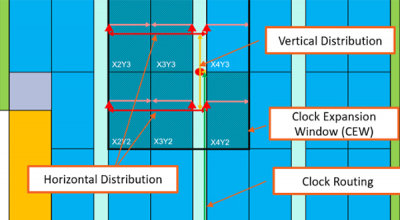

适用于 SSIT 的 Versal Fmax 取决于时钟拓扑结构扩展范围

适用于 SSIT 的 Versal Fmax 取决于时钟拓扑结构扩展范围

使用“时钟校准去歪斜”时,在 Vivado 中会显示下列消息以指明是否启用该功能特性

Versal SYSMON 是通过 Vivado 中的 CIPS GUI 来配置的。您可以通过寄存器存取来对 SYSMON 进行寻址

本文将演示如何在 IP integrator 内使用 CIPS Wizard 设置“System Monitor”(系统监控器)

在Versal Advanced IO Wizard中,所包含的PLL的去歪斜电路可能导致数据速率较高时出现建立时间

Vitis 库可在支持 AI 引擎的 Versal 器件上加速高级医疗成像在低时延情况下,提供高达 1000 FPS 的帧速率

本文则着重探讨 JTAG TDO 用例

3月23日,由AMD举办的在线研讨会上,我们将详细为您介绍这款最新发布的医疗成像库

Versal 系列的DMA axi bridge模式可以在PL的QDMA IP或者在CPM的QDMA IP中选中