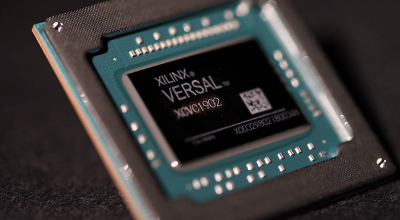

AMD Xilinx Versal™自适应SoC助力三星第二代SmartSSD处理功能再升级

judy 在 周四, 07/21/2022 - 10:31 提交

相较三星传统SSD固态硬盘,CPU利用率可高达97%,处理时间减少逾50%,功耗降低70%。

相较三星传统SSD固态硬盘,CPU利用率可高达97%,处理时间减少逾50%,功耗降低70%。

今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

PCIe 仿真需要Endpoint 模型和Root Port 模型协同工作。用户一般可以采用购买BFM/VIP 来模拟对端模型也可以自己设计对端模型

面向不同应用,Versal家族有AI Core, AI Edge , AI RF,Prime, Premium,HBM,六个系列、名字看起来是不是十分复杂?今天让我们来和您好好唠唠Versal系列这兄弟姐妹六系列!

本章旨在演示如何基于 Versal™ 来构建同时使用 SmartLynq+ 模块和高速调试端口 (HSDP) 的系统。

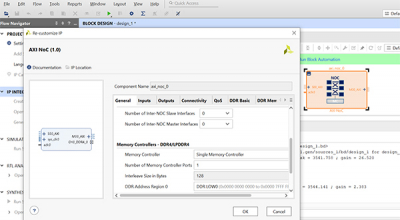

本章演示了如何利用 Vivado® 工具并使用 PL AXI GPIO 来创建嵌入式设计。其中还演示了如何在 Versal 器件上为基于 Arm® Cortex™-A72 核的 APU 配置并构建 Linux 操作系统。

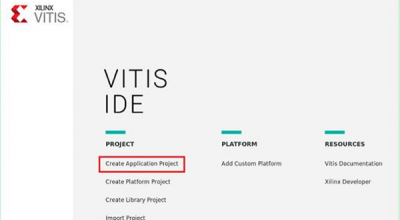

本章用于演示如何为 Versal™ ACAP 集成和加载引导加载程序、裸机应用(针对 APU/RPU)和 Linux 操作系统。

本文提供了一个基于VCK190 ES1开发板和2021.1 Vivado/Vitis的例子,用来简单介绍在Versal里实现数据从PL 经过 FPD CCI 到达 NoC DDR的一致性传输。

本教程对应目标为 Versal ACAP VCK190 和 VMK 180 评估板。本教程中的示例已使用 VCK190 ES1 评估板经过测试。要使用本教程,您需要具备以下硬件项,这些硬件项均随附于该评估板中