Versal嵌入式设计教程:启动和配置

judy 在 周日, 04/24/2022 - 15:57 提交

本章用于演示如何为 Versal™ ACAP 集成和加载引导加载程序、裸机应用(针对 APU/RPU)和 Linux 操作系统。

本章用于演示如何为 Versal™ ACAP 集成和加载引导加载程序、裸机应用(针对 APU/RPU)和 Linux 操作系统。

本文提供了一个基于VCK190 ES1开发板和2021.1 Vivado/Vitis的例子,用来简单介绍在Versal里实现数据从PL 经过 FPD CCI 到达 NoC DDR的一致性传输。

本教程对应目标为 Versal ACAP VCK190 和 VMK 180 评估板。本教程中的示例已使用 VCK190 ES1 评估板经过测试。要使用本教程,您需要具备以下硬件项,这些硬件项均随附于该评估板中

本文档旨在提供有关将赛灵思 Vivado® Design Suite 流程应用于 Versal™ VMK180/VCK190 评估板的指示信息。所使用的工具为 Vivado Design Suite 和 Vitis™ 统一软件平台 2020.2 版。

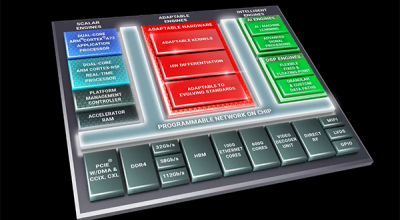

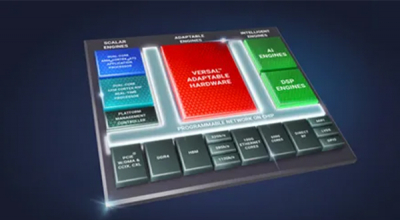

过去几年里,计算行业见证了数据的大规模爆发以及机器学习( ML )与 AI 应用的激增。其结果是对更高吞吐量和实时计算能力愈发强烈的需求,与此同时还要保持灵活应变能力,以便跟上不断演进的工作负载需求和不断变化的协议。

使用 Vivado 2021.1 或更高版本实现的所有 Versal 集成内存控制器接口都支持 2D 眼图扫描功能。2D Eye Scan 可用于检查每个字节通道的健康状况,并允许图形比较以快速识别布局和开发板相关问题。

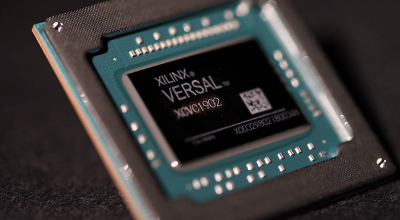

赛灵思 Versal™ 自适应计算加速平台 (ACAP) 设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。遵循这些步骤和最佳实践进行操作,这将有助于以尽可能最快且最高效的方式实现期望的设计目标。

从金融、电信、工业、消费到航空航天与国防以及汽车,如今,“同步”这个概念,在所有行业无处不在。众多应用完全离不开同步;本文将探讨其中的部分应用并根据这些示例来分享同步这个概念。此外,本文的第二部分将研讨同步的两个关键技术指标:精度与准确性和集成。

基于 Xilinx Versal 的波束成型解决方案可在 Xilinx 7nm Versal 平台上逐步实现 5G FR1( 7.125GHz 以下)64T64R/32T32R 波束成型解决方案。