Versal ACAP XPE 设计咨询 - 电源排序更改

judy 在 周一, 02/20/2023 - 14:25 提交

在某些情况下,部分 VCCO 能与该序列中的其它电源轨共享

在某些情况下,部分 VCCO 能与该序列中的其它电源轨共享

Versal XPIO IOLOGIC 包含 IDDR、IFD、IDELAY、ODDR、OFD 和 ODELAY

尽管超声波技术能提供显著优势,但医疗设备制造商正发现

本文介绍了如何开启Versal最基本的XilSEM功能。

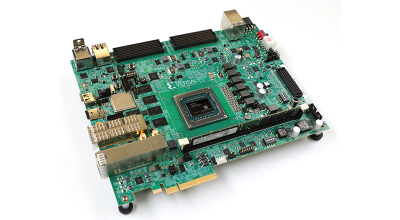

Versal™ 是由多个高度耦合的可配置块组成的自适应计算加速平台 (ACAP)

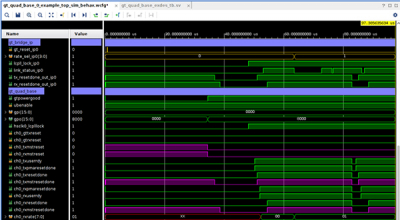

本篇博文侧重于提供 Versal™ GTY 仿真示例、演示 GTY 如何解复位以及如何执行速率变更。

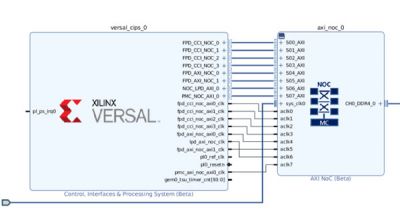

本篇博文旨在演示如何通过 NoC 从 Versal™ 应用处理单元 (APU) 访问 AXI BRAM。

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径,并展示了其易用性和增强型向导。

本篇设计咨询涵盖了 Versal GTM 复位不稳定问题

AMD AI 研发团队入选的两篇论文侧重基于 Versal 异构计算平台的 AI 处理器架构设计,充分发挥 Versal 平台的算力和灵活性优势。