Vivado中增量编译与设计锁定

judy 在 周一, 01/25/2021 - 09:10 提交

所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线。这样做的好处是显而易见的,即节省运行时间,能提高再次布局、布线结果的可预测性,并有助于时序收敛。

所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和网线等直接复用,而对发生改变的部分重新布局、布线。这样做的好处是显而易见的,即节省运行时间,能提高再次布局、布线结果的可预测性,并有助于时序收敛。

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加

在数据的传输过程中,我们经常可以碰见双沿传输数据到FPGA,或者FPGA传输双沿数据给外部芯片,最常见的例子就是DDR芯片。这里说明一下,FPGA内部处理的数据都是单沿数据,那么双沿数据的变换只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。

Vivado硬件平台更新后Vitis工程如何快捷更新

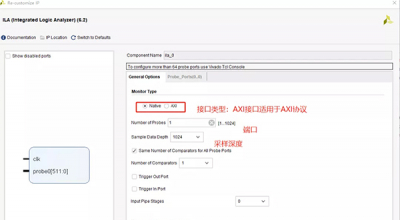

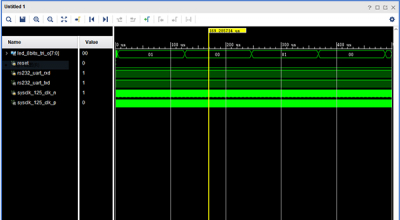

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

我在xdc文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

本文介绍如何导出硬件平台, 并启动SDK开发应用程序及板级支持包(BSP)。