【线上活动】Xilinx Adapt China: Vivado

judy 在 周一, 03/29/2021 - 11:40 提交

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

4月22日-23日,赛灵思举办 Adapt China:Vivado专场,特邀Vivado专家团队,与您分享 Vivado 在设计自动化集成、IP子系统复用和加速设计收敛等方面的方法和技巧。

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

本视频着重介绍了 Vivado Design Suite 2020.2 版中的新增功能,包括操作系统和器件支持、高级别增强功能以及加速设计集成、实现与验证相关的各项改进措施。

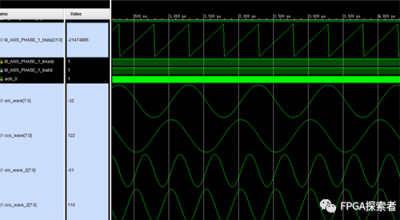

本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

vivado提供了DDS IP核可以输出正余弦波形,配置方法如下

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。今天介绍的是Vivado的三种常用IP核

在Vivado使用过程中,会碰到如下情况:设计代码已经编写完成,且仿真、综合或实现中的某一步骤已经通过,不需要再修改。此时可能需要添加一些注释代码,或者调整代码的格式,而任何修改都会导致状态更改为“Out of date”,提示用户更新设计。如何才能在不重新运行综合或实现的情况下解决这个问题?

vivado建立的工程经常会出现版本升级而导致的IP核锁定情况,本文以vivado 2019.2的版本打开旧版本为例,介绍两种更新方法

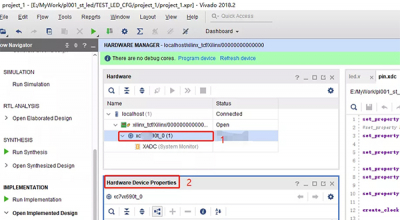

都知道FPGA的启动方式有很多种,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分为主从即Master和Slave(时钟由FPGA的管脚发出,专用的CCLK信号为主,否则为从,有的配置有辅助时钟EMCCLK,它由外部的晶振提供,从FPGA的EMCCLK输入,经过专用的逻辑,再从CCLK管脚输出给想用的器件,),那么问题来了,配置失败怎么办呢??????????????

本文描述了在 Vivado® Design Suite 中创建、打包和重用自定义 IP 的过程。详细介绍了如何使用创建和包装 IP 向导来包装自定义 IP,包括 IP 集成器中开发的 IP 和高级 IP 包装选项。